# **CASPER Toolflow**

Release 0.1

Collaboration for Astronomy Signal Processing and Electronics R

## Setup

| 1 What is mlib_devel?                        | 3   |

|----------------------------------------------|-----|

| 2 Using mlib_devel                           | 5   |

| 3 Updating an Existing Toolflow Installation | 7   |

| 4 mlib_devel directory structure             | 9   |

| Python Module Index                          | 181 |

| Index                                        | 183 |

Welcome to the documentation for  $mlib\_devel$ , the CASPER Toolflow!

Setup 1

2 Setup

## CHAPTER 1

What is mlib\_devel?

The mlib\_devel repository contains a set of FPGA DSP libraries and programming tools developed and maintained by the Collaboration for Astronomical Signal Processing and Electronics Research (CASPER). Within the collaboration, this collection of software is affectionately referred to as *The Toolflow*.

The CASPER toolflow allows you to generate signal processing designs using MATLAB's graphical programming tool Simulink. These designs can be turned into FPGA bitstreams and loaded onto a variety of supported hardware platforms to perform real-time digital signal processing systems. CASPER also provides a Python software library for interacting with running designs: casperfpga.

| $\cap$ L | AF     | D٦ |   | Q  |   |

|----------|--------|----|---|----|---|

| VΙ       | $\Box$ |    | ᆫ | ıι | _ |

Using mlib\_devel

For more information about installing and using the CASPER Toolflow, see the project's documentation.

CASPER also maintain a set of tutorials, designed to introduce new users to the toolflow.

## CHAPTER 3

## Updating an Existing Toolflow Installation

You can always update your installation of *mlib\_devel* by pulling updated code from this repository. If you do this, chances are you'll need to update your Simulink models to match your new *mlib\_devel* libraries. A script is provided to automate this process. With your model open and active, in your MATLAB prompt, run

update\_casper\_blocks(bdroot)

This script will resynchronize every CASPER block in your design with its latest library version. Depending on the size of your model, it may take many minutes to complete! As always, back up your designs before attempting such a major operation. And, if you experience problems, please raise Github issues!

## CHAPTER 4

## mlib\_devel directory structure

casper\_library Simulink DSP libraries

xps\_library Simulink libraries for tool-flow supported modules (ADC interfaces, Ethernet cores, etc.)

xps\_base HDL code and Xilinx EDK wrappers used in older (ROACH2 and earlier) versions of the toolflow.

docs Sphinx documentation for the software in this project.

*jasper\_library* Python and MATLAB scripts required to drive the compilation process. Also platform-dependent configuration information and source-code for IP modules used by the toolflow in the following directories.

*platforms* YAML files defining the compile parameters and physical constraints of CASPER-supported FPGA platforms.

golden Golden boot images for FPGA platforms which require them.

hdl\_sources HDL source files for all toolflow-suppled modules (eg. ADC interfaces, Ethernet cores, etc.).

sw Codebase for embedded software processors used by the toolflow

*yellow\_blocks* Python classes for each yellow block in the simulink *xps\_library*.

## 4.1 Setup

The software stack you will require to use the toolflow will depend what hardware you are targeting. Older hardware (ROACH2 and earlier) use the older Xilinx software (ISE) which forces the use of different tools.

The current compatibility matrix is below:

(Note that official support for ROACH plaforms is no longer provided, however this version of *mlib\_devel* contains all ROACH related documentation and ROACH tutorials can be found here)

| Hard-    | Operating Sys- | Matlab Ver- | Xilinx Ver-   | mlib_devel branch / | Python Ver- |

|----------|----------------|-------------|---------------|---------------------|-------------|

| ware     | tem            | sion        | sion          | commit              | sion        |

| ROACH1/2 | Ubuntu 14.04   | 2013b       | ISE 14.7      | branch: roach       | Python 2.7  |

| SKARAB   | Ubuntu 16.04   | 2018a       | Vivado        | branch: master      | Python 3    |

|          |                |             | 2019.1.1      |                     |             |

| SNAP     | Ubuntu 16.04   | 2018a       | Vivado        | branch: master      | Python 3    |

|          |                |             | 2019.1.1      |                     |             |

| Red      | Ubuntu 16.04   | 2018a       | Vivado        | branch: master      | Python 3    |

| Pitaya   |                |             | 2019.1.1      |                     |             |

| VCU118   | Ubuntu 16.04   | 2018a       | Vivado        | branch: master      | Python 3    |

|          |                |             | 2019.1.1      |                     |             |

| VCU128   | Ubuntu 16.04   | 2018a       | Vivado        | branch: master      | Python 3    |

|          |                |             | 2019.1.1      |                     |             |

| ZCU111   | Ubuntu 16.04   | 2018a       | Vivado        | branch: master      | Python 3    |

|          |                |             | 2019.1.1      |                     |             |

| SNAP2    | Ubuntu 16.04   | 2016b       | Vivado 2016.4 | branch: master      | Python 3    |

The recommended OS is Ubuntu as it is what the majority of the collaboration are using. This makes it easier for us to support you. If you are so inclined, you could also use Red Hat, but we definitely do not support Windows. You are welcome to try but you will be on your own. You could always run Linux in a VM although this will increase your compile times.

Please refer to the setup links below for more information on setting up the toolflow.

## 4.1.1 Setup Links

- 1. Installing the Toolflow

- 2. Installing Matlab

- 3. Installing Xilinx Vivado

- 4. Configuring the Toolflow

- 5. Running the Toolflow

#### Installing the Toolflow

This page explains how to install the CASPER tools and what supporting software is required to run them.

#### **Getting the right versions**

The toolflow is very sensitive to mis-matching software versions. The current compatibility matrix of software versions is below:

(Note that official support for ROACH plaforms is no longer provided, however this version of mlib\_devel contains all ROACH related documentation and ROACH tutorials can be found here)

Other software combinations may work, but these are the tested configurations. The master branch is usually updated once a year. Between updates, code with newer features can be found in the <code>casper-astro-soak-test</code> branch. This branch can usually be used in place of the <code>master</code> branch for platforms which support <code>master</code>. However, be aware that <code>casper-astro-soak-test</code> is likely to be less stable. Please report any bugs you encounter via github's issue tracker.

#### **Pre-requisites**

#### 1. MATLAB

MATLAB installation instructions are available here, or, contact whoever manages your software installations. You will need to install both MATLAB and Simulink.

#### 2. Xilinx Vivado

This is available from xilinx.com and will require a license. If you are part of an academic institution you may be eligible for free licenses via the Xilinx University Program. Vivado install instructions are available here.

#### 3. Python

Compiling for supported platforms requires Python 3 and pip3. If you don't have these already you can probably install them in Ubuntu environments by opening a terminal and running the command apt-get install python3 python3-pip.

We thoroughly recommend using a virtual environment to separate the version of Python and its libraries the toolflow uses from the rest of your system.

To create a Python 3 virtual environment:

```

# change directory to where you want the virtual environment to live

cd /home/user/work

# install virtualenv using pip3

sudo pip3 install virtualenv

# create a Python 3 virtual environment

virtualenv -p python3 casper_venv

# to activate the virtual environment:

source casper_venv/bin/activate

# to deactivate the virtual environment:

deactivate

```

#### **Obtaining the Toolflow**

Clone the toolflow from the mlib\_devel git repository.

```

# Clone the mlib_devel repository. Replace <branch_name> with the branch

# supported by your chosen platform.

# Eg. for master you should run:

# git clone -b master https://github.com/casper-astro.mlib_devel

git clone -b <branch_name> https://github.com/casper-astro/mlib_devel

```

This could take a while – the repository is several hundred megabytes. If you want, you can save some time by adding the –-depth=1 flag to the above command. This will only download the current version of the repository, rather than its full git history.

Next, move into the mlib\_devel repository you have just created, activate your virtual environment (if using one) and download any Python dependencies you need by installing the requirements.txt file. The downloaded dependencies will be installed within the virtual environment separate to the rest of your system.

```

cd mlib_devel

source /home/user/work/casper_venv/bin/activate

pip3 install -r requirements.txt

```

You may need to run the pip3 install command as an administrator if you are using the system-maintained python installation instead of a virtual environment.

#### Configuring the toolflow

You now have all the software you need to start building your designs. However, you'll still need to specify some local configuration details which will depend on how you carried out your installation. See Configuring the Toolflow for more details.

#### How to install Matlab

This section explains How To install Matlab R2013b and R2016b.

#### How to Install R2013b

- 1. OS Required/suggested: Ubuntu 14.04 LTS

- 2. Ubuntu 14.04. Using Nautilius, click on R2013b\_UNIX.iso and extract to "Installs/Matlab2013b".

- 3. Ubuntu 14.04. Open a terminal < ctrl + alt + T>. You will need to install the JRE (Java Runtime Environment) if you don't have it. Type sudo apt-get install openjdk-7-jre at the prompt and press enter.

- 4. Terminal: You will now need to backup file "libstdc++.so.6" and link to file "libstdc++.so.6.0.13". Type in cd ~/Installs/Matlab2013b/bin/glnxa64 and press enter.

- 5. Terminal: Type sudo mv libstdc++.so.6 libstdc++.so.6\_bu and enter. The file should now be backed up.

- 6. Terminal: Type sudo ln -s libstdc++.so.6.0.13 libstdc++.so.6 and press enter. The file should now be linked.

- 7. Terminal: set the matlab environment variable to call java 7. Type export MATLAB\_JAVA="/usr/lib/jvm/java-7-openjdk-amd64/jre and press enter. Type echo \$MATLAB\_JAVA to make sure the new path is set.

- 8. Terminal: Make sure the java is executable. Type cd ~/Installs/Matlab2013b and press enter. Type chmod +x sys/java/jre/glnxa64/jre/bin/java and press enter.

- 9. Terminal: You will now need to invoke the installer. Type sudo ./install -javadir /usr/lib/jvm/java-7-openjdk-amd64/jre at the prompt and press enter.

- 10. The MathWorks Installer GUI should pop up. Select "Install without using the Internet" and select "Next".

- 11. You will be requested to sign the "License Agreement" page. Click "Yes" and then click "Next".

- 12. You will be requested to fill in the file installation key for your license. The Matlab Administrator should of provided a license and file installation key. If not, make sure you get one from him/her. Type in the file installation key and press "Next". I choose to install my license file under "~/Matlab".

- 13. You will then be requested for the "Installation Type". Click on the "Typical" radio button and press "Next".

- 14. You will then need to specify the installation folder. I choose "/opt/Matlab/R2013b". Press "Next". If the folder does not exist then click "Yes" to create it.

- 15. You will then be required to confirm your installation settings. If happy then press "Install" else press "Back" and then return to this step when happy.

- 16. You will be informed that your installation may require additional configuration skips. This can be ignored. Click "Next".

- 17. You will be informed that the installation is complete. Make sure Activate Matlab is ticked and click "Next".

- 18. It is now time to Activate MathWorks Software. A "MathWorks Software Activation" window will pop up. Click on the "Activate manually without the internet" and press "Next".

- 19. Click on the "Enter the full path to your license file, including the file name:" and browse to the license file (\*.lic) and click "Select". Then press "Next". If all goes well then you will receive a message that says "Activation is complete.". Click "Finish".

- 20. Open another terminal and navigate to the "opt" folder and remember to change user and group to your username with the following command: sudo chown <username>:<username> Matlab -R

- 21. Terminal: Navigate to the "home" folder and remember to change user and group to your username with the following command: sudo chown <username>:<username> .matlab -R

- 22. It will be a good idea to create an Matlab R2013b startup script file on your Desktop with the following lines:

```

#!/bin/bash

cd /opt/Matlab/R2013b/bin/

./matlab

```

```

NB: Make sure the file is executable and that the nautilius documentation navigator is set to run the script.

```

- 1. Run the script and the Matlab IDE will launch. You can now select the required Matlab m files (\*.m) and continue.

- 2. In order to run the ISE-flow of the CASPER tools, please see here

#### **How To Install R2016b**

- 1. OS Required/suggested: Ubuntu 14.04 LTS, Ubuntu 16.04 LTS (with tweaks), Red Hat 6.6 (Santiago).

- 2. Ubuntu 14.04. Using Nautilius, click on "R2016b\_glnxa64\_dvd1.iso" and extract to "Installs/Matlab2016b".

- 3. Ubuntu 14.04. Open a terminal < ctrl + alt + T> and type cd ~/Installs and then type chmod +w Matlab2016b/ -R. This will give all the files in the Matlab2016b folder write access.

- 4. Ubuntu 14.04. Using Nautilius, click on "R2016b\_glnxa64\_dvd2.iso" and extract to "Installs/Matlab2016b".

- 5. Open a terminal <ctrl + alt + T> and type cd  $\sim$ /Installs/Matlab2016b/,then sudo ./install and enter.

- 6. The MathWorks Installer GUI should pop up. Select "Use a File Installation Key" and select "Next".

- 7. You will be requested to sign the "License Agreement" page. Click "Yes" and then click "Next".

- 8. You will be requested to fill in the file installation key for your license. The Matlab Administrator should of provided a license and file installation key. If not, make sure you get one from him. Type in the file installation key and press "Next". I choose to install my license file under "~/Matlab".

- 9. You will then need to specify the installation folder. I choose "/opt/Matlab/R2016b". Press "Select" and then "Next".

- 10. You will then see a "Product Selection" window. Make sure that all products are ticked and select "Next".

- 11. You must then decide where you want the symbolic links to your Matlab scripts to be stored. I chose the default location "/usr/local/bin".

- 12. You will then be required to confirm your installation settings. If happy then press "Install" else press "Back" and then return to this step when happy.

- 13. You will be informed that your installation may require additional configuration skips. This can be ignored. Click "Next".

- 14. You will be informed that the installation is complete. Make sure Activate Matlab is ticked and click "Next".

- 15. It is now time to Activate MathWorks Software. A "MathWorks Software Activation" window will pop up. Click on the "Activate manually without the internet" and press "Next".

- 16. Click on the "Enter the full path to your license file, including the file name:" and browse to the license file (\*.lic) and click "Select". Then press "Next". If all goes well then you will receive a message that says "Activation is complete.". Click "Finish".

- 17. Open another terminal and navigate to the "opt" folder and remember to change user and group to your username with the following command: sudo chown <username>:<username> Matlab -R

- 18. Terminal: Navigate to the "home" folder and remember to change user and group to your username with the following command: sudo chown <username>:<username> .matlab -R

- 19. It will be a good idea to create an Matlab R2016b startup script file on your Desktop with the following lines:

```

#!/bin/bash

cd /opt/Matlab/R2016b/bin/

./matlab

```

- 1. Run the script and the Matlab IDE will launch. You can now select the required Matlab m files (\*.m) and continue.

- 2. In order to run Matlab with the Casper tools please look at the CASPER read the docs page: https://caspertoolflow.readthedocs.io/en/latest/jasper\_documentation.html.

#### How To Install R2018a

- 1. OS Required/suggested: Ubuntu 14.04 LTS/Ubuntu 16.04 LTS.

- 2. Ubuntu 16.04. Using Nautilius, click on "R2018a\_glnxa64\_dvd1.iso" and extract to "Installs/Matlab2018a".

- 3. Ubuntu 16.04. Open a terminal < ctrl + alt + T> and type cd  $\sim$ /Installs and then type chmod +w Matlab2018a/ -R. This will give all the files in the Matlab2018a folder write access.

- 4. Ubuntu 16.04. Using Nautilius, click on "R2018a\_glnxa64\_dvd2.iso" and extract to "Installs/Matlab2018a".

- 5. Open a terminal <ctrl + alt + T> and type cd  $\sim$ /Installs/Matlab2018a/,then sudo ./install and enter.

- 6. The MathWorks Installer GUI should pop up. Select "Use a File Installation Key" and select "Next".

- 7. You will be requested to sign the "License Agreement" page. Click "Yes" and then click "Next".

- 8. You will be requested to fill in the file installation key for your license. The Matlab Administrator should of provided a license and file installation key. If not, make sure you get one from him. Type in the file installation key and press "Next". I choose to install my license file under "~/Matlab".

- 9. You will then need to specify the installation folder. I choose "/opt/Matlab/R2018a". Press "Select" and then "Next".

- 10. You will then see a "Product Selection" window. Make sure that all products are ticked and select "Next".

- 11. You must then decide where you want the symbolic links to your Matlab scripts to be stored. I chose the default location "/usr/local/bin".

- 12. You will then be required to confirm your installation settings. If happy then press "Install" else press "Back" and then return to this step when happy.

- 13. You will be informed that your installation may require additional configuration skips. This can be ignored. Click "Next".

- 14. You will be informed that the installation is complete. Make sure Activate Matlab is ticked and click "Next".

- 15. It is now time to Activate MathWorks Software. A "MathWorks Software Activation" window will pop up. Click on the "Activate manually without the internet" and press "Next".

- 16. Click on the "Enter the full path to your license file, including the file name:" and browse to the license file (\*.lic) and click "Select". Then press "Next". If all goes well then you will receive a message that says "Activation is complete.". Click "Finish".

- 17. Open another terminal and navigate to the "opt" folder and remember to change user and group to your username with the following command: sudo chown <username>:<username> Matlab -R

- 18. Terminal: Navigate to the "home" folder and remember to change user and group to your username with the following command: sudo chown <username>:<username> .matlab -R

- 19. It will be a good idea to create an Matlab R2016b startup script file on your Desktop with the following lines:

```

#!/bin/bash

cd /opt/Matlab/R2018a/bin/

./matlab

```

- 1. Run the script and the Matlab IDE will launch. You can now select the required Matlab m files (\*.m) and continue.

- 2. Install the R2018a update pack: "r2018a-update-6.tar.gz" by unpacking the tar.gz file and following the install instructions "r2018a-updates-install-instructions.pdf" for linux.

- 3. In order to run Matlab with the Casper tools please look at the CASPER read the docs page: https://caspertoolflow.readthedocs.io/en/latest/jasper\_documentation.html.

#### How to install Xilinx Vivado

This section explains How To install Vivado 2016.2, 2016.4 and 2018.2.

#### How to Install 2016.x

- 1. OS Required/suggested: Ubuntu 14.04 LTS, Ubuntu 16.04 LTS (with tweaks) and Red Hat 6.6 (Santiago). There was an issue using Ubuntu 12.04 LTS, which caused the DocNav utility to crash.

- 2. Click/double click on the Xilinx\_Vivado\_SDK\_2016.2\_0605\_1.tar.gz file in the Ubuntu Nautilius document navigator and choose a folder to extract the files to. I use "home/Installs" in this document. If you use something different then remember to replace "Installs" with your directory name.

- 3. Ubuntu 14.04. Open a terminal < ctrl + alt + T>. Change directory to the following folder: cd Installs/Xilinx\_Vivado\_SDK\_2016.2\_0605\_1

- 4. Terminal: Type sudo ./xsetup and press enter. This application needs to be installed with root privileges otherwise the installation will not install properly. You will be prompted for the sudo password. Enter this and press enter.

- 5. The Vivado Installer GUI will pop up. The GUI might explain that there is a new version available, but ignore that and press "Continue" and then "Next" to commence with the installation process.

- 6. Read the terms and conditions page and when happy tick "I agree" for all three tick boxes. Then click "Next".

- 7. Select the "Vivado HL\_System Edition" radio button and select "Next".

- 8. You will then be required to select which tools you want to install with the Vivado Design Edition. I selected "Software Development Kit", "Ultrascale+" and "Zynq UltraScale + MPSoC". The rest of the boxes were ticked (except Cable Drivers), so I have decided to install the complete set of tools available. Make sure that "DocNav" is ticked if you want access to the documentation that Xilinx has provided. This is highly recommended, as the documentation is part of the Ultrafast design methodology. Press "Next".

- 9. Select where you want to install the Vivado tool set. I am using the default opt/Xilinx folder. I have also ticked the "Create program group entries" and "create desktop shortcuts" buttons. This is not necessary though. Press "Next".

- 10. A window will pop up offering to create the opt/Xilinx directory if it does not exist. Select "Yes".

- 11. A window with the "Installation Summary" will be displayed showing what tools will be installed and where they will be stored on your drive. If you are happy press "Install", otherwise press "Back" and edit your previous settings.

- 12. Wait until the Xilinx Software Install window states that the "Installation completed successfully" and select "OK".

- 13. Open another terminal and navigate to the opt/ folder and remember to change user and group to your username with the following command: sudo chown <username>:<username> Xilinx -R

- 14. Terminal: Navigate to the home folder and remember to change user and group to your username with the following command: sudo chown <username>:<username> .Xilinx -R

- 15. DocNav will not work unless you follow the steps highlighted in the text file: set\_up\_vivado\_2015.1\_on\_ubuntu\_14.04 (Doc Nav section only). Install the i386 architecture and then install the missing libraries. All the commands are highlighted in the attached file.

- 16. DocNav will now open, but you won't be able to open the documentation until you have made the following link. Using the terminal type in cd /opt/Xilinx/Vivado/2016.2/ids\_lite/ISE/lib/lin64 and press enter.

- 17. Using the terminal, type in mv libstdc++.so.6 libstdc++.so.6bu and press enter. Now type in ln -s /usr/lib/x86\_64-linux-gnu/libstdc++.so.6 ./libstdc++.so.6 and pressenter. The libstdc++.so.6 file will now be properly linked and DocNav should work.

- 18. It will be a good idea to create a vivado startup script file on your Desktop with the following lines:

```

#!/bin/bash

cd /opt/Xilinx/Vivado/2016.2/bin/

./vivado

```

- 19. Run the script and the Vivado IDE will launch. You can now select the required Xilinx Vivado project file (\*.xpr) and continue.

- 20. It is now time to install the license for Vivado. Create a Xilinx folder in your home directory using the nautilius documentation navigator: home/<user name>/Xilinx and copy the vivado license file provided by your administrator to this location.

- 21. Load the license using the Vivado License Manager". If not already open click on "Help" -> "Manage License...". Click "Load License" and then click on "Copy License...". Navigate to the license file (\*.lic) in the home/<user name>/Xilinx folder. Press "Open" and when the license installation was successful then press "OK".

- 22. To confirm that the license file was successful, click on "View License Status" and make sure a list of Tools/IP is read back and that the license is still valid. Once this is done then close the "Vivado License Manager" by

clicking on the red cross at the top left of the window. You will be prompted if you want to close the "Vivado License Manager". Click "Yes".

#### Optional: Install USB Drivers for JTAG

Note: this will only be used by toolflow/yellow block developers and is not required for standard use of the toolflow

The most reliable way to install the JTAG cable drivers is to use the drivers provided with ISE.

A folder containing all the files required has been uploaded in the same folder as this document: linux\_jtag\_cable\_drivers.tar.gz. This also includes a useful installation script that prepares the files and places them in the correct directories.

#### Instructions:

- Extract the contents of the file linux\_jtag\_cable\_drivers.tar.gz

- Run: sudo ./install.sh(NB!: Must run as sudo)

It may be a good idea to power your PC/lap top down and then up again as the USB drivers may not take affect until this happens. In my case, I plugged a stick drive into the USB and then ejected that and connected the Xilinx Platform Cable USB module. Once this was done then the status LED illuminated and I was able to configure the FPGA via JTAG.

#### How to Install 2018.x

- 1. OS Required/suggested: Ubuntu 16.04 LTS.

- 2. Click/double click on the Xilinx\_Vivado\_SDK\_2018.2\_0614\_1954.tar.gz file in the Ubuntu Nautilius document navigator and choose a folder to extract the files to. I use "home/Installs" in this document. If you use something different then remember to replace "Installs" with your directory name.

- 3. Ubuntu 16.04. Open a terminal < ctrl + alt + T>. Change directory to the following folder: cd Installs/ Xilinx\_Vivado\_SDK\_2018.2\_0614\_1954

- 4. Terminal: Type sudo ./xsetup and press enter. This application needs to be installed with root privileges otherwise the installation will not install properly. You will be prompted for the sudo password. Enter this and press enter.

- 5. The Vivado Installer GUI will pop up. The GUI might explain that there is a new version available, but ignore that and press "Continue" and then "Next" to commence with the installation process.

- 6. Read the terms and conditions page and when happy tick "I agree" for all three tick boxes. Then click "Next".

- 7. Select the "Vivado HL System Edition" radio button and select "Next".

- 8. You will then be required to select which tools you want to install with the Vivado Design Edition. I selected "Software Development Kit", "Ultrascale+" and "Zynq UltraScale+ MPSoC". The rest of the boxes were ticked (except Cable Drivers), so I have decided to install the complete set of tools available. Make sure that "DocNav" is ticked if you want access to the documentation that Xilinx has provided. This is highly recommended, as the documentation is part of the Ultrafast design methodology. Press "Next".

- 9. Select where you want to install the Vivado toolset. I am using the default opt/Xilinx folder. I have also ticked the "Create program group entries" and "create desktop shortcuts" buttons. This is not necessary though. Press "Next".

- 10. A window will pop up offering to create the opt/Xilinx directory if it does not exist. Select "Yes".

- 11. A window with the "Installation Summary" will be displayed showing what tools will be installed and where they will be stored on your drive. If you are happy press "Install", otherwise press "Back" and edit your previous settings.

- 12. Wait until the Xilinx Software Install window states that the "Installation completed successfully" and select "OK".

- 13. Open another terminal and navigate to the opt/ folder and remember to change user and group to your username with the following command: sudo chown <username>:<username> Xilinx -R

- 14. Terminal: Navigate to the home folder and remember to change user and group to your username with the following command: sudo chown <username>:<username> .Xilinx -R

- 15. If DocNav does not work, then try follow the steps highlighted in the text file: set\_up\_vivado\_2015.1\_on\_ubuntu\_14.04 (Doc Nav section only). Install the i386 architecture and then install the missing libraries. All the commands are highlighted in the attached file.

- 16. DocNav may open, but it is possible you won't be able to read the documentation until you have made the following link first try and read the documentation via DocNav though. Using the terminal type in cd /opt/Xilinx/Vivado/2016.2/ids\_lite/ISE/lib/lin64 and press enter.

- 17. If you still can't access the documentation via DocNav: Using the terminal, type in mv libstdc++. so.6 libstdc++.so.6bu and press enter. Now type in ln -s /usr/lib/x86\_64-linux-gnu/libstdc++.so.6 ./libstdc++.so.6 and pressenter. The libstdc++.so.6 file will now be properly linked and DocNav should work.

- 18. It will be a good idea to create a vivado startup script file on your Desktop with the following lines:

```

#!/bin/bash

cd /opt/Xilinx/Vivado/2018.2/bin/

./vivado

```

- 19. Run the script and the Vivado IDE will launch. You can now select the required Xilinx Vivado project file (\*.xpr) and continue.

- 20. It is now time to install the license for Vivado. Create a Xilinx folder in your home directory using the nautilius documentation navigator: home/<user name>/Xilinx and copy the vivado license file provided by your administrator to this location.

- 21. Load the license using the Vivado License Manager". If not already open click on "Help" -> "Manage License...". Click "Load License" and then click on "Copy License...". Navigate to the license file (\*.lic) in the home/<user name>/Xilinx folder. Press "Open" and when the license installation was successful then press "OK".

- 22. To confirm that the license file was successful, click on "View License Status" and make sure a list of Tools/IP is read back and that the license is still valid. Once this is done then close the "Vivado License Manager" by clicking on the red cross at the top left of the window. You will be prompted if you want to close the "Vivado License Manager". Click "Yes".

#### **Optional: Install USB Drivers for JTAG**

Note: this will only be used by toolflow/yellow block developers and is not required for standard use of the toolflow

A folder containing all the files required has been uploaded in the same folder as this document: linux\_jtag\_cable\_drivers.tar.gz. This also includes a useful installation script that prepares the files and places them in the correct directories.

**Instructions:**

- Extract the contents of the file linux\_itag\_cable\_drivers.tar.gz

- Run: sudo ./install.sh (NB!: Must run as sudo)

It may be a good idea to power your PC/lap top down and then up again as the USB drivers may not take affect until this happens. In my case, I plugged a stick drive into the USB and then ejected that and connected the Xilinx Platform Cable USB module. Once this was done then the status LED illuminated and I was able to configure the FPGA via JTAG.

#### Configuring the Toolflow

If you have successully installed the toolflow and its dependencies, it is now time to configure the flow to suit your specific environment. The toolflow needs to know where dependencies like MATLAB and Xilinx tools have been installed. Other site-dependent parameters may also need to be defined.

#### The startsg script

A startup script – startsg – is provided as part of the toolflow repository. This script can be used in two ways:

- If executed (i.e. /path/to/mlib\_devel/startsg): start MATLAB with the correctly defined library paths.

- If sourced (i.e. source /path/to/mlib\_devel/startsg): configure software paths without starting MATLAB.

The former method is what you should do if you want to start a Simulink design, or open an existing one.

The latter method is useful if you want to run parts of the toolflow outside of MATLAB (eg.  $exec_flow.py$ ) or run Xilinx tools (eg. vivado) directly from the command line.

#### Specifying local details

The startsg script is generic. You should not need to modify it. The script does not require that the Matlab and Xilinx tools be installed in specific locations, but it does require that you provide it with a few details about your local installation. This is done by creating a startsg.local file that defines a few key variables needed by startsg. Two essential variables are:

- $\bullet$  MATLAB\_PATH the path to the directory where MATLAB was installed

- XILINX\_PATH the path to the directory where Xilinx tools were installed

#### Optional variables:

- PLATFORM Used by the Xilinx tools to select suitable runtime binaries for your system. If not specified, it will be defaulted to lin64, indicating a 64-bit Linux operating system. This is the only configuration the collaboration tests.

- XILINXD\_LICENCE\_FILE The path to your Xilinx software license if it exists in a non-standard location.

- JASPER\_BACKEND the type of Xilinx tools you want to use to implement your design. Supported options are vivado or ise. The default is vivado, which is correct for all CASPER-supported platforms. (Note: ise is the Xilinx tool used for ROACH1/ROACH2 designs, however official support for ROACH platforms is no longer provided).

- CASPER\_PYTHON\_VENV\_ON\_START The path to your Python virtual environment (if one is being used). This will activate the virtual environment on load.

Other variables: Depending on your operating system, and MATLAB / Xilinx quirks, you may need to specify other generic OS variables. For example, with MATLAB 2018a and Ubuntu 16.04, it is necessary to over-ride the default MATLAB libexpat library to a newer version. To do this you can set the LD PRELOAD variable.

Here is a sample startsg.local file:

```

export XILINX_PATH=/opt/Xilinx/Vivado/2019.1

export MATLAB_PATH=/usr/local/MATLAB/R2018a

export PLATFORM=lin64

export JASPER_BACKEND=vivado

# over-ride the MATLAB libexpat version with the OS's one.

# Using LD_PRELOAD=${LD_PRELOAD}:"..." rather than just LD_PRELOAD="..."

# ensures that we preserve any other settings already configured

export LD_PRELOAD=${LD_PRELOAD}:"/usr/lib/x86_64-linux-gnu/libexpat.so"

# Activate a custom python environment on load

export CASPER_PYTHON_VENV_ON_START=/home/user/work/casper_venv

```

Since this configuration refers to your specific installation environment, in general it shouldn't be committed to the mlib\_devel repository. In fact, the repository is configured to ignore changes to any files with names beginning startsg. If you really want to commit your local configuration file, you can do this, but it's helpful to call it something other than startsg.local, (eg. startsg.local.example or startsg.local.my-server-name) so as not to conflict with other users, all of whom will have similar files with different contents.

#### Using startsg

By default, executing (or sourcing) the startsg script will use variables defined in the configuration file startsg. local residing in the same directory as startsg. However, you can use a specific configuration by specifying one as an argument to startsg. This can be useful if you want to store configurations for multiple versions of MATLAB / Xilinx tools.

For example:

```

$ ./startsg  # Uses startsg.local if one exists in the_

current directory

$ ./mlib_devel/startsg  # Uses startsg.local if one exists in ./mlib_

cdevel/

$ ./startsg startsg.local.use_vivado_2016  # Uses the startsg.local.use_vivado_16_

configuration file

```

#### Symlink for convenience

Running startsg from the mlib\_devel directory (where it lives) will start MATLAB with mlib\_devel as the current directory. Hopefully you store your models somewhere outside mlib\_devel (which should contain only the CASPER *libraries*), in which case after running startsg you will need to navigate within MATLAB to the directory where your model files live. To avoid this minor annoyance, you can create a symbolic link to startsg in your application directory (i.e. where your model file lives). When running startsg via this symlink, MATLAB will start up with your application directory as the current directory and also run the optional casper\_startup.m file if one exists.

To configure such a symlink you should run

```

# Go to the directory you store your models in.

# You should place a startsg.local file here.

cd /directory/where/my/models/are

# Create the symbolic link

ln -s /directory/where/mlib_devel/is/startsg startsg

# Run startsg from your model directory

./startsg my.startsg.local

```

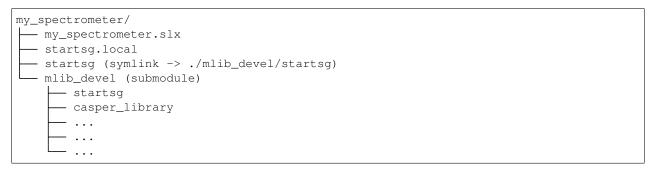

This model of operating works particularly well when using git submodules to store a copy of mlib\_devel alongside your models. Using submodules in this way ensures that whoever downloads your models can also easily obtain the version of mlib\_devel they were originally compiled against.

In this case, your directory structure will look something like:

#### **Running the Toolflow**

- 1. There are two ways of working with the Vivado-based CASPER toolflow. You can do this initially with the MATLAB GUI to compile the front end and then handle the middleware and backend generation using Python or you can run everything in Python. The former stage is more for design and debugging (steps 2-11) and the later stage (steps 12-15) is for the final tested and working design. This How-to will cover both methods.

- 2. **Matlab/Python method:** Using the terminal, type the following under "mlib\_devel": ./startsg It is currently not possible to compile for Altera or Lattice FPGAs. This script will source all the relevant Matlab and Xilinx paths, run matlab and start the system generator. Wait until the Matlab GUI has opened and Matlab is ready.

- 3. **Matlab/Python method:** In the Matlab command window, type the following: simulink. This will start simulink. Wait until the Simulink window has opened.

- 4. **Matlab/Python method:** In the Simulink Library Browser, click on the "open model or library" icon in the tab and select where your desired simulink file is (\*.slx). There are some test files under "jasper\_library/test\_models". I use "test\_snap.slx" for this How To. Once the file has been selected, click "Open". The "test\_snap" design should open in the Simulink window.

- 5. **Matlab/Python method:** Click the simulink design window ("test\_snap") and press the following: "Ctrl + D". This will update the simulink model and check for warnings or errors. Make sure there are no errors or warnings. A window should pop up if this is the case.

- 6. **Matlab/Python method:** In the Matlab command window terminal, type the following: jasper\_frontend. This will generate the yellow block peripheral file and run the system generator. Wait until the "XSG generation complete. Complete. Run 'exec\_flow.py -m ....' message is displayed.

- 7. Matlab/Python method: In the Matlab Command Window, cut the following text from it: python .../ exec\_flow.py -m ... --middleware --backend --software .... The matlab generation process is now complete and now it is time to switch to Python.

- 8. **Matlab/Python method:** Open a new terminal <CTRL+ALT+T>, and source the following files from the "mlib\_devel" directory: startsg This is an important step, because the Xilinx and Matlab paths will not be specified properly and "exec\_flow.py" will fail to run if this is not done.

- 9. Matlab/Python method: Using the terminal, paste the "python exec\_flow.py...." command that was cut earlier from Matlab, in the terminal: python exec\_flow.py -m ... --middleware --backend --software. This command will execute the middleware, which calls the yellow block constructors, creates the top.v file and generates the yaml file, which contains all the parameters needed for the backend to compile. The backend reads the yaml file and builds a list of sources, constraints, generates the constraints file and the tcl file. This tcl file is used by Vivado to compile the top.v file and all other relevant source files. This generates a bit and binary file, which is used to configure the FPGA. The software reads the binary file and generates a bof and fpg file. The arguments passed to exec\_flow.py will be explained in more detail below when dealing with the Python method.

- 10. **Matlab/Python method:** Using the terminal, wait until the design has finished compiling. Vivado compiles should indicate that there are no timing violations. Check the slack times for the setup and hold reports. They should not be negative. If they are then your design is not meeting timing and some changes will need to be made to your design.

- 11. **Matlab/Python method:** The output directories are generated where the \*.slx file sits. For example, building for test\_snap.slx results in the following directories being generated under jasper\_library/test\_models/test\_snap/:

- sysgen/: contains the system generator files,

- outputs/: contains the bof and fpg files, and

- myproj/: contains the Vivado projects files, source files, synth results and implementation results. The bin and bit files are also stored here.

**NB:** Instead of running "jasper\_frontend" from the Matlab command window, you can run "jasper", which will do all the above steps from 6) to now, but all display output will be routed through the Matlab Command window.

- 12. **Python method:** Before I explain this method it is important to explain how the "exec\_flow" command works and the arguments that are passed to it.

- The exec\_flow, which stands for "execution flow" can either run the whole flow or just parts of the flow

depending on the needs of the user.

- The Vivado compile is done using project mode only.

- I have already explained the --middleware, --backend and --software arguments in step 9) above.

- There is also a --perfile and --frontend argument, which is not needed in the Matlab/Python method, but is required for the Python method.

- The --perfile and --frontend arguments run the yellow block peripheral file generation and the system generator compile, respectively. It is identical to running jasper\_frontend from the command window in Matlab see Matlab/Python method above.

- Below is a list of the exec\_flow arguments.

- --perfile Runs the front end peripheral file generation. If not specified, then it won't generate

the peripheral file.

- --frontend This compiles the front end IP, which basically runs the system generator. If not specified, then the compile will not be run.

- --middleware This runs the toolflow middle process. If not specified, then this process will not be run.

- --backend This runs the backend compilation i.e. Xilinx Vivado. If not specified, then this

process will not be run.

- --software This runs the software compilation generates a \*.bof and \*.fpg file. If not specified, then this process will not be run.

- --be This specifies the type of backend to be run. This is "-be vivado", but provision has been made for other backends. If this is not specified, then the default is the Vivado backend.

- --jobs The number of processor cores to run the compile with. If this is not specified, the default is 4. You need to make sure that your processor has at least 4 threads if this is to work.

- m The absolute path and filename of the \*.slx file (Simulink model) to compile. If not specified, the

default is "/tools/mlib\_devel/jasper\_library/test\_models/test.slx". I would suggest always specifying

this.

- -c This is the build directory. The default is the same directory as the \*.slx file (Simulink model). I don't normally specify this.

- --synth\_strat Specify a Synthesis Strategy for your compile. The options are as follows, as provided by Vivado 2019.1.1:

- \* Flow\_AreaOptimized\_high

- \* Flow\_AreaOptimized\_medium

- \* Flow\_AreaMultThresholdDSP

- \* Flow\_AlternateRoutability

- \* FFlow\_PerfOptimized\_high

- \* Flow\_PerfThresholdCarry

- \* Flow\_RuntimeOptimized

- --impl\_strat Specify an Implementation Strategy for your compile. The options are as follows, as provided by Vivado 2019.1.1:

- \* Performance\_Explore

- \* Performance\_ExplorePostRoutePhysOpt

- \* Performance\_ExploreWithRemapx

- \* Performance\_WLBlockPlacement

- \* Performance\_WLBlockPlacementFanoutOpt

- \* Performance\_EarlyBlockPlacement

- \* Performance\_NetDelay\_high

- \* erformance\_NetDelay\_low

- \* Performance\_Retiming

- \* Performance\_ExtraTimingOpt

- \* Performance\_RefinePlacement

- \* Performance\_SpreadSLLs

- \* Performance\_BalanceSLLs

- \* Performance\_BalanceSLRs

- \* Performance HighUtilSLRs

- \* Congestion\_SpreadLogic\_high

- \* Congestion\_SpreadLogic\_medium

- \* Congestion\_SpreadLogic\_low

- \* Congestion\_SSI\_SpreadLogic\_high

- \* Congestion\_SSI\_SpreadLogic\_low

- \* Area Explore

- \* Area\_ExploreSequential

- \* Area\_ExploreWithRemap

- \* Power\_DefaultOpt

- \* Power\_ExploreArea

- \* Flow\_RunPhysOpt

- \* Flow\_RunPostRoutePhysOpt

- \* Flow\_RuntimeOptimized

- \* Flow Quick

Here are some examples of how to run the command:

This will run the whole process, except will not generate a fpg and bof file for programming.

This will run the whole process.

This will run the front end peripheral file generation and IP compile process using the Vivado system generator.

```

python .../exec_flow.py -m /home/<username>/mlib_devel/jasper_library/test_models/ \rightarrow test_snap.slx --perfile --frontend

```

- 13. **Python method:** Open a new terminal <CTRL+ALT+T>, and source the following files from the mlib\_devel directory:

- source startsg startsg.local

- This is an important step, because the Xilinx and Matlab paths will not be specified properly and exec\_flow.py will fail to run.

- 14. **Python method:** Using the terminal, run the complete "exec\_flow" command:

```

python .../exec_flow.py -m /home/<username>/mlib_devel/jasper_library/test_models/

-test_snap.slx --perfile --frontend --middleware --backend --software

```

Feel free to add or remove arguments as you wish or need. The design should run through the toolflow generation process to completion. Once complete, the Vivado compile should report any errors, e.g. timing issues. The Vivado compile will determine if timing is met or not and display this to the screen. The user will need to monitor the slack time variable to see whether the compile has met timing or not. If the slack time is negative then timing is not met and if the slack time is positive for both setup and hold timing then the design has met the timing requirements.

- 15. **Python method:** The output directories are generated where the \*.slx file sits. I used "test\_snap.slx", hence the following directories were generated under jasper\_library/test\_models/test\_snap/:

- sysgen/: contains the system generator files,

- outputs/: contains the bof and fpg files, and

- myproj/: contains the Vivado projects files, source files, synthesis results and implementation results.

The bin and bit files are also stored here.

## 4.2 Documentation

- CASPER Tutorials

- Block Documentation

- Toolflow Documentation

- Toolflow Sourcecode

- casperfpga Sourcecode

#### 4.2.1 Block Documentation

#### **Contents**

- Signal Processing Blocks

- Communication Blocks

- System Blocks

### **Signal Processing Blocks**

```

adder_tree (Adder Tree)

barrel_switcher (Barrel Switcher)

bit_reverse (Bit Reverser)

cmult_4bit_br* (Conjugating Complex 4-bit Multiplier Implemented in BlockRAM)

cmult_4bit_br (Complex 4-bit Multiplier Implemented in BlockRAM)

cmult_4bit_em* (Conjugating Complex 4-bit Multiplier Implemented in Dedicated Multipliers)

cmult_4bit_em (Complex 4-bit Multiplier Implemented in Embedded Multipliers)

cmult_4bit_sl* (Conjugating Complex 4-bit Multiplier Implemented in Slices)

cmult_4bit_sl (Complex 4-bit Multiplier Implemented in Slices)

complex_addsub (Complex Adder/Subtractor)

c_to_ri (Complex to Real/Imaginary)

DDS (Direct Digital Synthesizer)

dec_fir (Decimating FIR Filter)

```

4.2. Documentation 25

```

delay_bram_en_plus (Enabled Delay in BlockRAM))

delay_bram_prog (Programmable Delay in BlockRAM)

delay_bram (Delay in BlockRAM)

delay_complex (Complex Delay)

delay slr (Delay in SLRs)

delay wideband prog (Programmable Wideband Delay Implemented in BlockRAM)

dram_vacc (DRAM Vector Accumulator)

dram_vacc_tvg (DRAM Vector Accumulator Test Vector Generator)

edge (Edge Detect Block)

fft_biplex_real_2x (Real-sampled Biplex FFT, with Output Demuxed by 2)

fft_biplex_real_4x (Real-sampled Biplex FFT, with Output Demuxed by 4)

fft (Complex FFT)

fft_wideband_real (Real-sampled Wideband FFT)

finedelay_fstop_prog (Programmable Fine delay along with Fringe Stop)

finedelay_fstop_prog_cordic (Programmable Fine delay with Fringe Stop using CORDIC block)

fir col (PFB FIR Column)

fir_dbl_col (PFB FIR Double Column)

fir_tap (PFB FIR Tap)

freeze_cntr (Freeze Counter)

lo_const (DC Local Oscillator)

lo_osc (Local Oscillator)

mixer (Mixer)

negedge (Negative Edge Detector)

partial delay (Partial Delay)

pfb fir real (Real-sampled Polyphase FIR Filter Frontend for PFB)

pfb_fir (Polyphase FIR Filter Frontend for PFB)

posedge (Positive Edge Detector)

power (Complex Data Power Calculator)

pulse ext (Pulse Extender)

rcmult (Real/Complex Multiplier)

reorder (Arbitrary Reorderer)

ri_to_c (Real/Imaginary to Complex)

square_transposer (Square Transposer)

stopwatch (Stopwatch)

sync_delay_en (Enabled Sync Delay)

sync_delay_proc (Programmable Sync Delay)

```

```

sync_gen (Parameterized Sync Generator)

win_x_engine (Windowed X-Engine)

xeng_tvg (X-Engine Test Vector Generator)

```

#### **Adder Tree**

Block: Adder Tree (adder\_tree)

Block Author: Aaron Parsons

Document Author: Aaron Parsons

#### **Contents**

- Summary

- Mask Parameters

- Ports

- Description

## **Summary**

Sums all inputs using a tree of adds and delays.

## **Mask Parameters**

| Parameter      | Variable | Description                                       |

|----------------|----------|---------------------------------------------------|

| No. of inputs. | n_inputs | The number of inputs to be summed.                |

| Add Latency    | latency  | The latency of each stage through the adder tree. |

#### **Ports**

| Port | Dir | Data Type | Description                                          |

|------|-----|-----------|------------------------------------------------------|

| sync | in  | Boolean   | Indicates the next clock cycle containing valid data |

| din  | in  | Inherited | A number to be summed.                               |

## **Description**

Sums all inputs using a tree of adds and delays. Total latency is  $ceil(log_2(n_inputs)) * latency$ .

4.2. Documentation 27

#### **Barrel Switcher**

Block: Barrel Switcher (barrel\_switcher)

**Block Author**: Aaron Parsons **Document Author**: Aaron Parsons

#### **Contents**

- Summary

- Mask Parameters

- Ports

- Description

## **Summary**

Maps a number of inputs to a number of outputs by rotating In(N) to Out(N+M) (where M is specified on the sel input), wrapping around to Out1 when necessary.

### **Mask Parameters**

| Parameter        | Variable | Description                                  |

|------------------|----------|----------------------------------------------|

| Number of inputs | n_inputs | The number of parallel inputs (and outputs). |

#### **Ports**

| Port     | Dir | Data Type | Description                                             |

|----------|-----|-----------|---------------------------------------------------------|

| sync     | in  | Boolean   | Indicates the next clock cycle contains valid data      |

| In       | in  | Inherited | The stream(s) to be transposed.                         |

| sync_out | out | Boolean   | Indicates that data out will be valid next clock cycle. |

| Out      | out | Inherited | The transposed stream(s).                               |

## **Description**

Maps a number of inputs to a number of outputs by rotating In(N) to Out(N+M) (where M is specified on the sel input), wrapping around to Out1 when necessary.

#### **Bit Reverser**

Block: Bit reverser (bit\_reverse)

**Block Author**: Aaron Parsons **Document Author**: Aaron Parsons

#### **Contents**

- Summary

- Mask Parameters

- Ports

- Description

### **Summary**

Reverses the bit order of the input. Input must be unsigned with binary point at position 0. Costs nothing in hardware.

#### **Mask Parameters**

| Parameter    | Variable | Description                       |

|--------------|----------|-----------------------------------|

| No. of bits. | n_bits   | Specifies the width of the input. |

#### **Ports**

| Port | Dir | Data Type | Description       |

|------|-----|-----------|-------------------|

| in   | in  | UFix_x_0  | The input signal. |

| out  | out | UFix_x_0  | The output.       |

#### **Description**

Reverses the bit order of the input. Input must be unsigned with binary point at position 0. Costs nothing in hardware.

## **Conjugate Complex 4-bit Multiplier BRAM**

**Block:** Conjugating Complex 4-bit Multiplier Implemented in Block RAM (cmult\_4bit\_br\*)

**Block Author:** ? **Document Author:** ?

#### **Contents**

- Summary

- Mask Parameters

- Ports

- Description

4.2. Documentation 29

#### **Summary**

Perform a conjugating complex multiplication  $(a + bi)(c \ di) = (ac + bd) + (bc \ ad)i$ . Implements the logic in Block RAM.

#### **Mask Parameters**

| Parameter          | Variable     | Description                       |

|--------------------|--------------|-----------------------------------|

| Multiplier Latency | mult_latency | The latency through a multiplier. |

| Add Latency        | add_latency  | The latency through an adder.     |

#### **Ports**

| Port | Dir | Data Type | Description                         |

|------|-----|-----------|-------------------------------------|

| a    | in  | Inherited | The real component of input 1.      |

| b    | in  | Inherited | The imaginary component of input 1. |

| С    | in  | Inherited | The real component of input 2.      |

| d    | in  | Inherited | The imaginary component of input 2. |

| real | out | Inherited | ac+bd                               |

| imag | out | Inherited | -ad+bc                              |

#### **Description**

Perform a conjugating complex multiplication  $(a + bi)(c \ di) = (ac + bd) + (bc \ ad)i$ . Implements the logic in Block RAM. Each 4 bit real multiplier is implemented as a lookup table with 4b+4b=8b of address.

#### **Complex 4-bit Multiplier BRAM**

**Block:** Complex 4-bit Multiplier Implemented in Block RAM (cmult\_4bit\_br)

**Block Author**: Block Author

**Document Author**: Document Author

#### **Contents**

- Summary

- Mask Parameters

- Ports

- Description

#### **Summary**

Perform a complex multiplication  $(a + bi)(c \ di) = (ac \ bd) + (ad + bc)i$ . Implements the logic in Block RAM.

#### **Mask Parameters**

| Parameter          | Variable     | Description                       |

|--------------------|--------------|-----------------------------------|

| Multiplier Latency | mult_latency | The latency through a multiplier. |

| Add Latency        | add_latency  | The latency through an adder.     |

#### **Ports**

| Port | Dir | Data Type | Description                         |

|------|-----|-----------|-------------------------------------|

| a    | in  | Inherited | The real component of input 1.      |

| b    | in  | Inherited | The imaginary component of input 1. |

| С    | in  | Inherited | The real component of input 2.      |

| d    | in  | Inherited | The imaginary component of input 2. |

| real | out | Inherited | ac-bd                               |

| imag | out | Inherited | ad-bc                               |

## **Description**

Each 4 bit real multiplier is implemented as a lookup table with 4b+4b=8b of address.

### **Conjugate Complex 4-bit Multiplier, Dedicated Multipliers**

$\textbf{Block: Conjugating Complex 4-bit Multiplier Implemented in Dedicated Multipliers. (\verb|cmult_4bit_em*|)}$

**Block Author**: ?

**Document Author**: Vinayak Nagpal

#### **Contents**

- Summary

- Mask Parameters

- Ports

- Description

## **Summary**

Perform a conjugating complex multiplication  $(a + bi)(c \ di) = (ac + bd) + (bc \ ad)i$ . Implements the logic in dedicated multipliers.

4.2. Documentation 31

#### **Mask Parameters**

| Parameter              | Variable     | Description                       |

|------------------------|--------------|-----------------------------------|

| Multiplier Latency     | mult_latency | The latency through a multiplier. |

| dd Latency add_latency |              | The latency through an adder.     |

#### **Ports**

| Port | Dir | Data Type | Description                         |

|------|-----|-----------|-------------------------------------|

| a    | in  | Inherited | The real component of input 1.      |

| b    | in  | Inherited | The imaginary component of input 1. |

| С    | in  | Inherited | The real component of input 2.      |

| d    | in  | Inherited | The imaginary component of input 2. |

| real | out | Inherited | ac+bd                               |

| imag | out | Inherited | -ad+bc                              |

## **Description**

Perform a conjugating complex multiplication  $(a + bi)(c \ di) = (ac + bd) + (bc \ ad)i$ . Implements the logic in dedicated multipliers. Each 4 bit real multiplier is implemented as a lookup table with 4b+4b=8b of address.

#### **Complex 4-bit Multiplier, Embedded Multipliers**

Block: Complex 4-bit Multiplier Implemented in Embedded Multipliers (cmult\_4bit\_em)

**Block Author:** ? **Document Author:** ?

#### **Contents**

- Summary

- Mask Parameters

- Ports

- Description

## **Summary**

Perform a complex multiplication  $(a + bi)(c \ di) = (ac \ bd) + (ad + bc)i$ . Implements the logic in embedded multipliers.

| Parameter          | Variable     | Description                       |

|--------------------|--------------|-----------------------------------|

| Multiplier Latency | mult_latency | The latency through a multiplier. |

| dd Latency         | add_latency  | The latency through an adder.     |

## **Ports**

| Port | Dir | Data Type | Description                         |

|------|-----|-----------|-------------------------------------|

| a    | in  | Inherited | The real component of input 1.      |

| b    | in  | Inherited | The imaginary component of input 1. |

| С    | in  | Inherited | The real component of input 2.      |

| d    | in  | Inherited | The imaginary component of input 2. |

| real | out | Inherited | ac-bd                               |

| imag | out | Inherited | ad+bc                               |

# **Description**

Perform a complex multiplication  $(a + bi)(c \ di) = (ac \ bd) + (ad + bc)i$ . Implements the logic in embedded multipliers. Each 4 bit real multiplier is implemented as a lookup table with 4b+4b=8b of address.

## **Conjugate Complex 4-bit Multiplier, Slices**

**Block:** Conjugating Complex 4-bit Multiplier Implemented in Slices (cmult\_4bit\_sl\*)

Block Author: Aaron Parsons

**Document Author**: Vinayak Nagpal

# **Contents**

- Summary

- Mask Parameters

- Ports

- Description

## **Summary**

Perform a conjugating complex multiplication  $(a + bi)(c \ di) = (ac + bd) + (bc \ ad)i$ . Implements the logic in Slices.

| Parameter          | Variable     | Description                       |

|--------------------|--------------|-----------------------------------|

| Multiplier Latency | mult_latency | The latency through a multiplier. |

| Add Latency        | add_latency  | The latency through an adder.     |

## **Ports**

| Port | Dir | Data Type | Description                         |

|------|-----|-----------|-------------------------------------|

| a    | in  | Inherited | The real component of input 1.      |

| b    | in  | Inherited | The imaginary component of input 1. |

| С    | in  | Inherited | The real component of input 2.      |

| d    | in  | Inherited | The imaginary component of input 2. |

| real | out | Inherited | ac+bd                               |

| imag | out | Inherited | -ad+bc                              |

# **Description**

Perform a conjugating complex multiplication  $(a + bi)(c \ di) = (ac + bd) + (bc \ ad)i$ . Implements the logic in Slices.

# **Complex 4-bit Multiplier, Slices**

**Block:** Complex 4-bit Multiplier Implemented in Slices (cmult\_4bit\_sl)

**Block Author**: Aaron Parsons

Document Author: Vinayak Nagpal

## **Contents**

- Summary

- Mask Parameters

- Ports

- Description

# **Summary**

Perform a complex multiplication  $(a + bi)(c \ di) = (ac \ bd) + (ad + bc)i$ . Implements the logic in Slices.

| Parameter          | Variable     | Description                       |

|--------------------|--------------|-----------------------------------|

| Multiplier Latency | mult_latency | The latency through a multiplier. |

| Add Latency        | add_latency  | The latency through an adder.     |

## **Ports**

| Port | Dir | Data Type | Description                         |

|------|-----|-----------|-------------------------------------|

| a    | in  | Inherited | The real component of input 1.      |

| b    | in  | Inherited | The imaginary component of input 1. |

| С    | in  | Inherited | The real component of input 2.      |

| d    | in  | Inherited | The imaginary component of input 2. |

| real | out | Inherited | ac-bd                               |

| imag | out | Inherited | ad+bc                               |

# **Description**

Perform a complex multiplication  $(a + bi)(c \ di) = (ac \ bd) + (ad + bc)i$ . Implements the logic in Slices.

# **Complex Adder/Subtractor**

**Block:** Complex Adder/Subtractor (complex\_addsub)

**Block Author**: Aaron Parsons **Document Author**: Ben Blackman

## **Contents**

- Summary

- Mask Parameters

- Ports

- Description

- Usage

# **Summary**

This block does a complex addition and subtraction of 2 complex numbers, a and b, and spits out 2 complex numbers, a+b and a-b.

| Parameter   | Variable    | Description                            |

|-------------|-------------|----------------------------------------|

| Bit Width   | BitWidth    | The number of bits in its input.       |

| Add Latency | add_latency | The latency of the adders/subtractors. |

## **Ports**

| Port | Dir | Data Type   | Description                                                                      |

|------|-----|-------------|----------------------------------------------------------------------------------|

| a    | IN  | 2*BitWidth  | The first complex number whose higher BitWidth bits are its real part and lower  |

|      |     | Fixed point | BitWidth bits are its imaginary part.                                            |

| b    | IN  | 2*BitWidth  | The second complex number whose higher BitWidth bits are its real part and lower |

|      |     | Fixed point | BitWidth bits are its imaginary part.                                            |

| a+b  | OUT | 2*BitWidth  | Upper BitWidth bits are real(a)+real(b). Lower BitWidth bits are imaginary(a)-   |

|      |     | Fixed point | imaginary(b).                                                                    |

| a-b  | OUT | 2*BitWidth  | Upper BitWidth bits are imaginary(a)+imaginary(b). Lower BitWidth bits are       |

|      |     | Fixed point | real(b)-real(a).                                                                 |

# **Description**

## **Usage**

The top output, a+b, is a complex output whose real part equals the sum of the real parts of a and b. The imaginary part of a+b equals the difference of the imaginary parts of a and b. The bottom output, a-b, is a complex output whose real part equals the sum of the imaginary parts of a and b. The imaginary part of a-b equals the difference of the real parts of b and a. The latency of this block is  $2*add_latency$ .

# **Complex to Real-Imag**

**Block:** Complex to Real-Imag Block (c\_to\_ri)

**Block Author**: Aaron Parsons **Document Author**: Aaron Parsons

## **Contents**

- Summary

- Mask Parameters

- Ports

- Description

# **Summary**

Outputs real and imaginary components of a complex input. Useful for simplifying interconnects. See also ri\_to\_c.

## **Mask Parameters**

| Parame-   | Vari-  | Description                                                                             |

|-----------|--------|-----------------------------------------------------------------------------------------|

| ter       | able   |                                                                                         |

| Bit Width | n_bits | Specifies width of real/imag components. Assumed equal for both components.             |

| Binary    | bin_pt | Specifies the binary point location in the real/imaginary components. Assumed equal for |

| Point     |        | both components.                                                                        |

## **Ports**

| Port | Dir | Data Type | Description                                                   |

|------|-----|-----------|---------------------------------------------------------------|

| c    | in  | UFix_x_0  | Complex input, real in MSB, imaginary in LSB.                 |

| r    | out | Fix_x_y   | Real signed output, binary point specified by parameter.      |

| i    | out | Fix_x_y   | Imaginary signed output, binary point specified by parameter. |

# **Description**

Outputs real and imaginary components of a complex input. Useful for simplifying interconnects. See also ri\_to\_c.

## **DDS**

Block: DDS (dds)

**Block Author**: Aaron Parsons **Document Author**: Ben Blackman

# **Contents**

- Summary

- Mask Parameters

- Ports

- Description

- Usage

# **Summary**

Generates sines and cosines of different phases and outputs them in parallel.

| Parameter                     | Variable | Description                           |

|-------------------------------|----------|---------------------------------------|

| Frequency Divisions (M)       | freq_div | Denominator of the frequency.         |

| Frequency (? /M * \$2\$ * pi) | freq     | Numerator of the frequency.           |

| Parallel LOs                  | num_lo   | Number of parallel local oscillators. |

| Bit Width                     | n_bits   | Bit width of the outputs.             |

| Latency                       | latency  | Description                           |

#### **Ports**

| Port | Dir | Data Type               | Description                                              |

|------|-----|-------------------------|----------------------------------------------------------|

| sinX | OUT | Fix_(n_bits)_(n_bits-1) | Sine output corresponding to the Xth local oscillator.   |

| cosX | OUT | Fix_(n_bits)_(n_bits-1) | Cosine output corresponding to the Xth local oscillator. |

# **Description**

## **Usage**

There are  $\sin$  and  $\cos$  outputs each equal to the minimum of  $num_lo$  and  $freq_div$ . If  $num_lo > = freq_div/freq$ , then the outputs will be  $lo_consts$ . Otherwise each output will oscillate depending on the values of  $freq_div$  and freq. If the outputs oscillate, then there will be a latency of latency and otherwise there will be zero latency.

#### **Decimating FIR Filter**

**Block:** Decimating FIR Filter (dec\_fir)

**Block Author**: Aaron Parsons

Document Author: Aaron Parsons, Ben Blackman

#### **Contents**

- Summary

- Mask Parameters

- Ports

- Description

- Usage

## **Summary**

FIR filter which can handle multiple time samples in parallel and decimates down to 1 time sample. If coefficiencts are symmetric, it will automatically fold before multiplying.

| Parameter           | Variable    | Description                                                                   |

|---------------------|-------------|-------------------------------------------------------------------------------|

| Number of Parallel  | n_inputs    | The number of time samples which arrive in parallel.                          |

| Streams             |             |                                                                               |

| Coefficients        | coeff       | The FIR coefficients. If this vector is symmetric, the FIR will automatically |

|                     |             | fold before multiplying.                                                      |

| Bit Width Out       | n_bits      | The number of bits in each real/imag sample of the complex number that is     |

|                     |             | output.                                                                       |

| Quantization Behav- | quantiza-   | The quantization behavior used in converting to the output bit width.         |

| ior                 | tion        |                                                                               |

| Add Latency         | add_latency | The latency of adders/converters.                                             |

| Mult Latency        | mult_latenc | yThe latency of multipliers.                                                  |

#### **Ports**

| Port     | Dir | Data Type               | Description                                        |

|----------|-----|-------------------------|----------------------------------------------------|

| sync_in  | IN  | boolean                 | Takes an impulse 1 cycle before input is valid.    |

| realX    | IN  | Fix_(n_bits)_(n_bits-1) | Real input X                                       |

| inagX    | IN  | Fix_(n_bits)_(n_bits-1) | Imaginary input X                                  |

| sync_out | OUT | boolean                 | Will be high the clock cycle before dout is valid. |

## **Description**

## **Usage**

User specifies the number of parallel streams to be decimated to one complex number. Inputs are multiplied by the coefficients and added together to form dout. Bit Width Out specifies the widths of the real and imaginary components of the complex number to be output (Ex. if Bit Width Out = 8, then dout will be 16 bits, 8 for the real and imaginary components).

# **Enabled Delay in BRAM**

Block: The Enabled Delay in BRAM Block (delay\_bram\_en\_plus)

**Block Author**: Aaron Parsons **Document Author**: Aaron Parsons

## **Contents**

- Summary

- Mask Parameters

- Ports

- Description

#### **Summary**

A delay block that uses BRAM for its storage and only shifts when enabled. However, BRAM latency cannot be enabled, so output appears bram\_latency clocks after an enable.

## **Mask Parameters**

| Parameter                                | Variable     | Description                                 |

|------------------------------------------|--------------|---------------------------------------------|

| Enabled Delays                           | DelayLen     | The length of the delay.                    |

| Extra (unenabled) delay for BRAM Latency | bram_latency | The latency of the underlying storage BRAM. |

#### **Ports**

| Port  | Dir | Data Type | Description                         |

|-------|-----|-----------|-------------------------------------|

| in    | in  | ???       | The signal to be delayed.           |

| en    | in  | ???       | To be asserted when input is valid. |

| out   | out | ???       | The delayed signal.                 |

| valid | out | ???       | Asserted when output is valid.      |

# **Description**

A delay block that uses BRAM for its storage and only shifts when enabled. However, BRAM latency cannot be enabled, so output appears bram\_latency clocks after an enable.

# **Programmable Delay in BRAM**

Block: The Programmable Delay in BRAM Block (delay\_bram\_prog)

**Block Author**: Aaron Parsons **Document Author**: Aaron Parsons

## **Contents**

- Summary

- Mask Parameters

- Ports

- Description

#### **Summary**

A delay block that uses BRAM for its storage and has a run-time programmable delay. When delay is changed, some randomly determined samples will be inserted/dropped from the buffered stream.

| Parameter                   | Variable     | Description                                           |

|-----------------------------|--------------|-------------------------------------------------------|

| Max Delay (2 <sup>?</sup> ) | MaxDelay     | The maximum length of the delay (i.e. the BRAM Size). |

| BRAM Latency                | bram_latency | The latency of the underlying storage BRAM.           |

## **Ports**

| Port  | Dir | Data Type | Description                             |

|-------|-----|-----------|-----------------------------------------|

| din   | in  | ???       | The signal to be delayed.               |

| delay | in  | ???       | The run-time programmable delay length. |

| dout  | in  | ???       | The delayed signal.                     |

# **Description**

A delay block that uses BRAM for its storage and has a run-time programmable delay. When delay is changed, some randomly determined samples will be inserted/dropped from the buffered stream.

## **Delay in BRAM**

**Block:** The Delay in BRAM Block (delay\_bram)

**Block Author**: Aaron Parsons **Document Author**: Aaron Parsons

## **Contents**

- Summary

- Mask Parameters

- Ports

- Description

## **Summary**

A delay block that uses BRAM for its storage.

## **Mask Parameters**

| Parameter    | Variable     | Description                                 |

|--------------|--------------|---------------------------------------------|

| Delay Length | DelayLen     | The length of the delay.                    |

| BRAM Latency | bram_latency | The latency of the underlying storage BRAM. |

| Port | Dir | Data Type | Description               |

|------|-----|-----------|---------------------------|

| in   | in  | ???       | The signal to be delayed. |

| out  | out | ???       | The delayed signal.       |

# **Description**

A delay block that uses BRAM for its storage.

# **Complex Delay**

Block: Complex Delay (delay\_complex)