# CASPER Tutorials Documentation Release 0.1

**Collaboration for Astronomy Signal Processing and Electronics R**

Mar 10, 2020

## **SNAP** Tutorials

| 1 | Tutorial Instructions | 3   |

|---|-----------------------|-----|

| 2 | Environment setup     | 291 |

Welcome to the CASPER tutorials page! Here you will find all the current tutorials for the ROACH, SNAP, SKARAB and Red Pitaya platforms.

It is recommended to start with the introduction tutorial for the platform of your liking, then do that platform's GBE tutorial and finally move onto the spectrometer or correlator tutorial or the next difficulty tutorial.

Currently there are five hardware platforms supported through the CASPER Community:

- 1. ROACH

- 2. ROACH2

- 3. SKARAB

- 4. SNAP

- 5. Red Pitaya

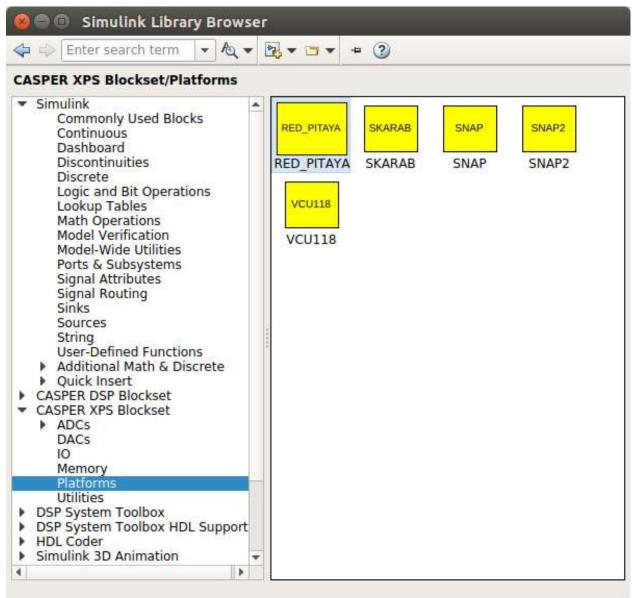

It is worth noting that even though SNAP, SKARAB and Red Pitaya require their firmwares to be developed using Xilinx's Vivado (as opposed to ISE), the **SNAP** tutorials are **very** similar to the ROACH/2 tutorials. In fact, the only real difference is the choice of hardware platform that is made in Simulink. This is done by selecting the **SNAP** Yellow Block in the Simulink library under *CASPER XPS Blockset -> Hardware Platforms*

# CHAPTER 1

## **Tutorial Instructions**

If you are new to astronomy signal processing, here is Tutorial 0: some basic introduction into astronomy signal processing. If you already have a lot of experience on it, you can go directly to the introduction tutorials below for CASPER FPGA design and implementation.

If you are a beginner, we recommend the Step-by-Step tutorials, however if you should get stuck, prefer a less tedious method of learning, or already have decent feel for these tools, links to Completed tutorials are available with commented models.

## 1.1 Vivado

## SNAP

- 1. Introduction Tutorial: Step-by-Step or Completed

- 2. 10GbE Tutorial: Step-by-Step or Completed

- 3. Spectrometer Tutorial Step-by-Step or Completed

- 4. Correlator Tutorial Step-by-Step or Completed

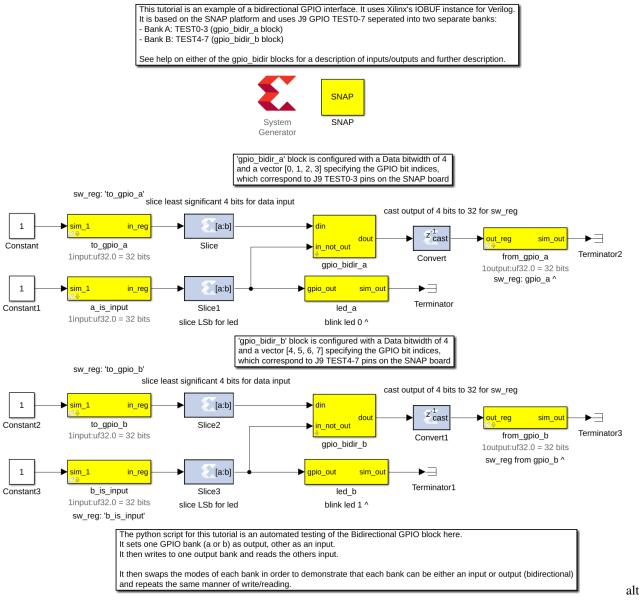

- 5. Yellow Block Tutorial: Bidirectional GPIO

## 1.1.1 Tutorial 1: Introduction to Simulink

In this tutorial, you will create a simple Simulink design using both standard Xilinx system generator blockset, as well as library blocks specific to CASPER boards (so-called "Yellow Blocks"). At the end of this tutorial, you will know how to generate an fpg file, program it to a CASPER FPGA board, and interact with your running hardware design using casperfpga via a Python Interface.

## **Creating Your Design**

#### **Create a New Model**

Start Matlab via executing the startsg command, as described here. This ensures that necessary Xilinx and CASPER libraries are loaded into your by Simulink. When MATLAB starts up, open Simulink by typing simulink on the MATLAB command line. Start a new model, and save it with an appropriate name. With Simulink, it is very wise to save early, and often.

There are some Matlab limitations you should be aware-of right from the start:

- Do not use spaces in your filenames or anywhere in the file path as it will break the toolflow.

- Do not use capital letters in your filenames or anywhere in the file path as it will break the toolflow.

- Beware block paths that exceed 64 characters. This refers to not only the file path, but also the path to any block within your design.

- For example, if you save a model file with a name ~/some\_really\_long\_filename.slx, and have a block called in a submodule the longest block path would be: some\_really\_long\_filename\_submodule\_block.

- If you use lots of subsystems, this can cause problems.

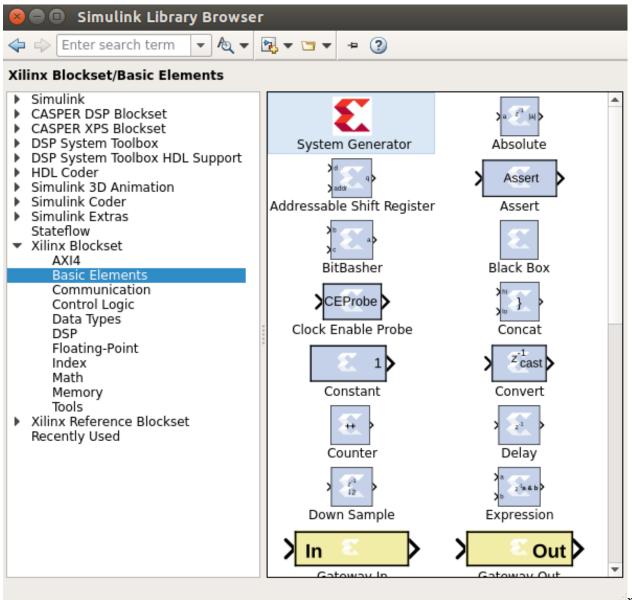

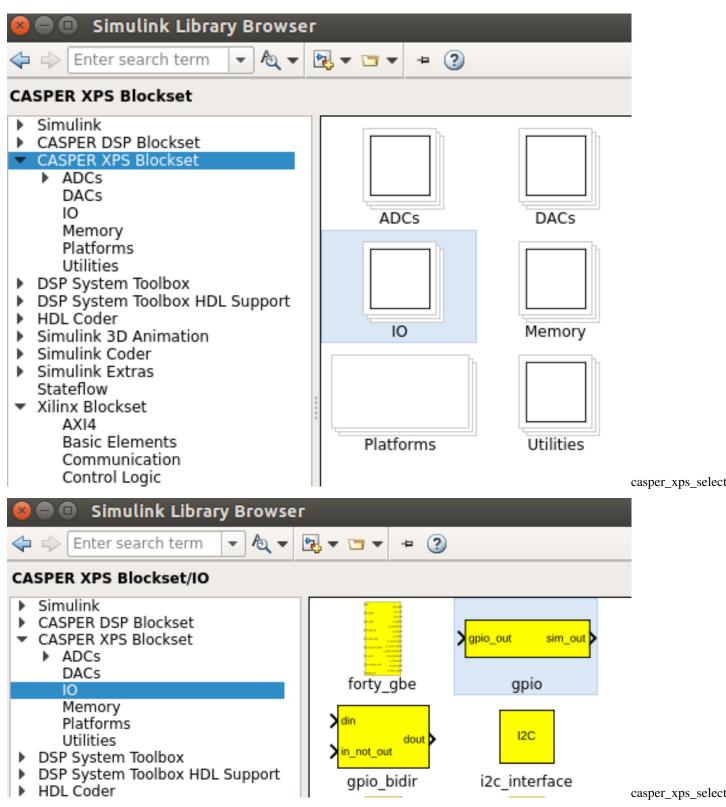

#### Library organization

There are three libraries which you will use when you design firmware in Simulink.

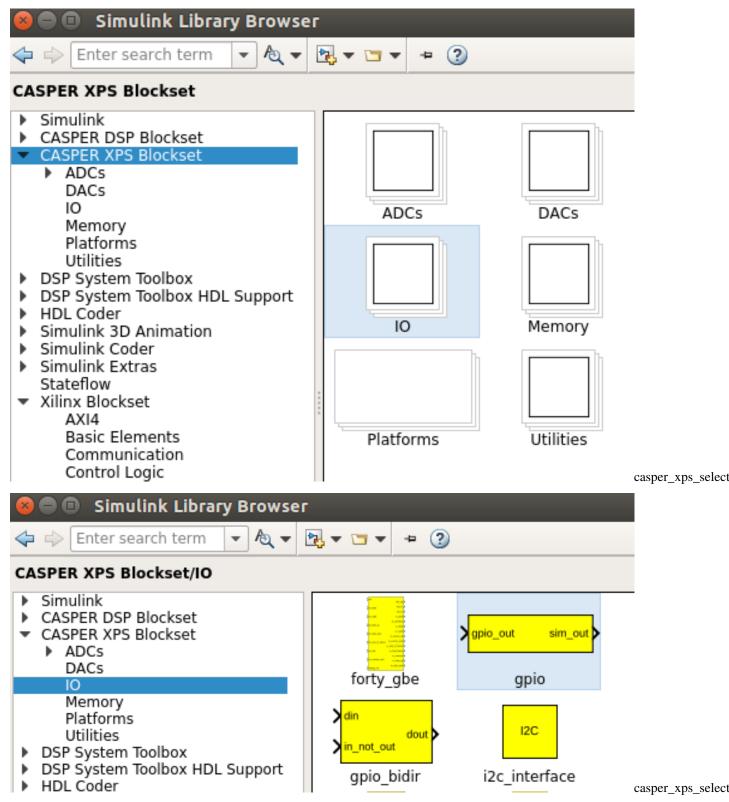

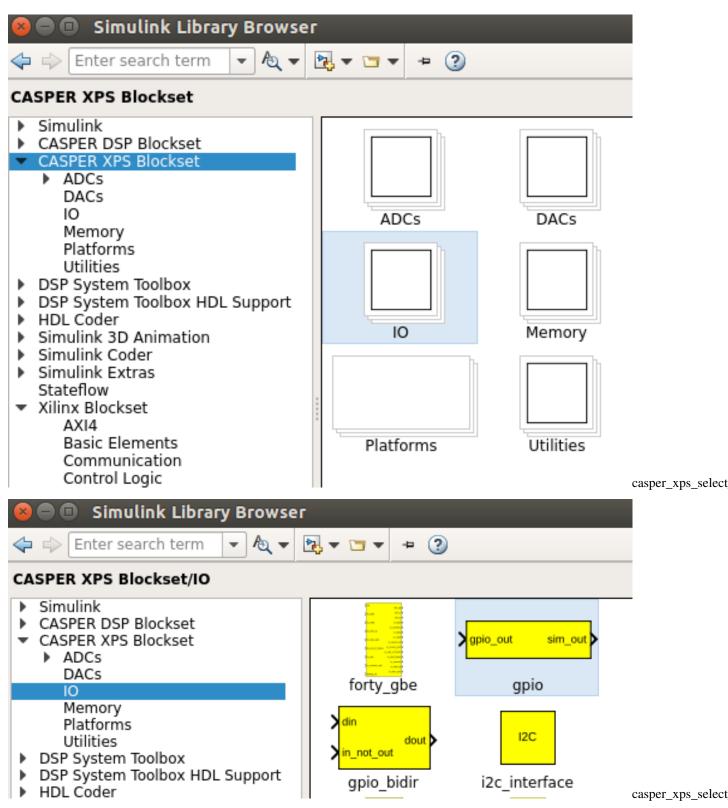

- 1. The **CASPER XPS Library** contains "Yellow Blocks" these are blocks which encapsulate interfaces to hardware (ADCs, Memory chips, CPUs, Ethernet ports, etc.)

- 2. The **CASPER DSP Library** contains (mostly green) blocks which implement DSP functions such as filters, FFTs, etc.

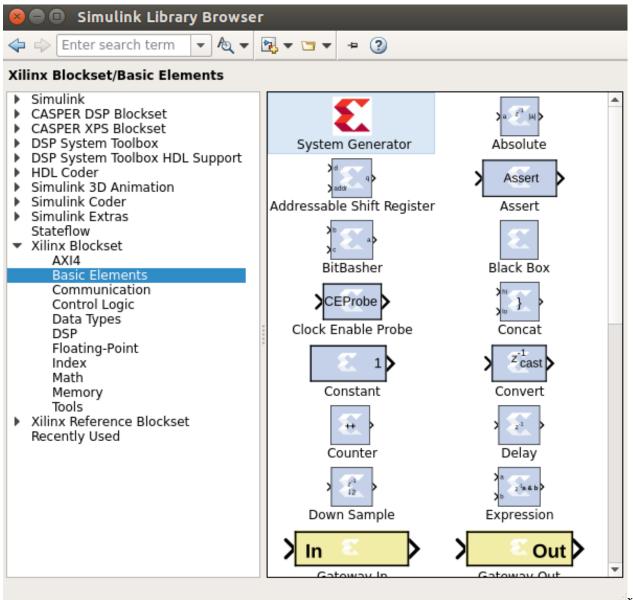

- 3. The **Xilinx Library** contains blue blocks which provide low-level functionality such as multiplexing, delaying, adding, etc. The Xilinx library also contains the super-special System Generator block, which contains information about the type of FPGA you are targeting.

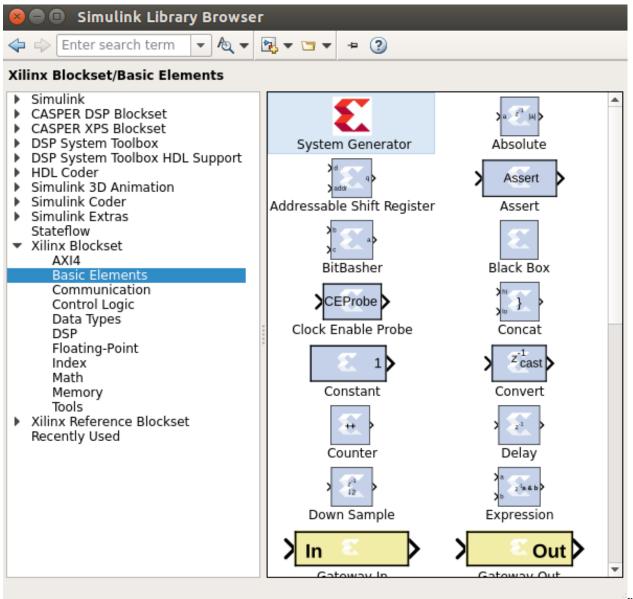

#### Add Xilinx System Generator and XSG core config blocks

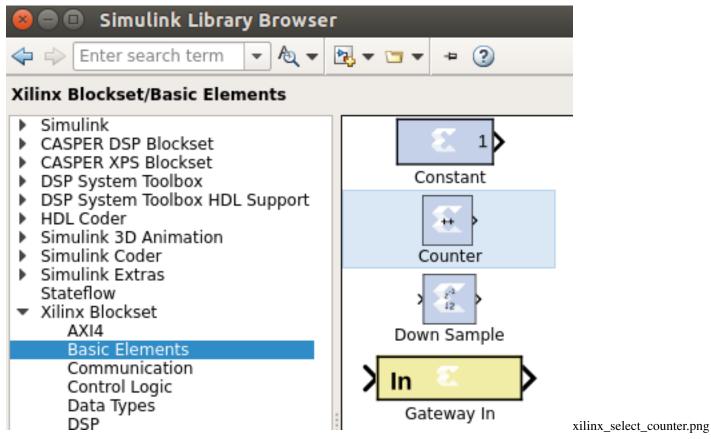

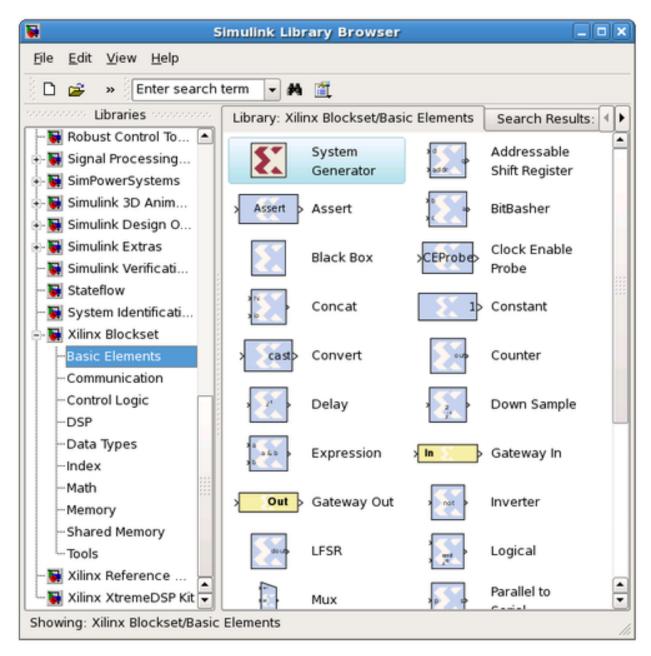

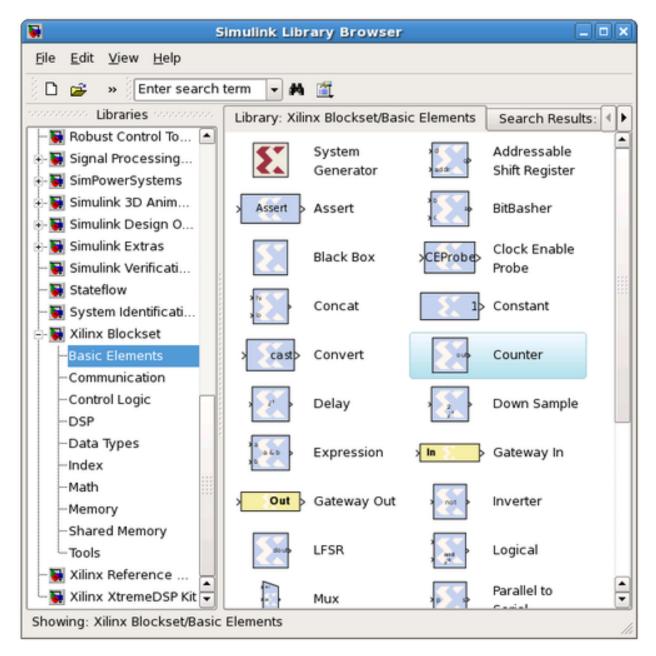

Add a System generator block from the Xilinx library by locating the Xilinx Blockset library's Basic Elements subsection and dragging a System Generator token onto your new file.

xilinx\_select\_sysg

Do not configure it directly, but rather add a platform block representing the system you care compiling for. These can be found in the CASPER XPS System Blockset library. For SNAP (and later) platforms, you need a block which matches the platform name, which can be found in the library under "platforms", as shown below.

| <ul> <li>■ ■ Simulink Library Browse</li> <li>□ ↓ Enter search term ▼ A ▼</li> </ul>                                                                                                                                                                                                                                                                                                                                           | r<br>🔁 🕶 📼 🕶 🌀                |                                  |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------|------------|

| <ul> <li>Simulink</li> <li>CASPER DSP Blockset</li> <li>CASPER XPS Blockset</li> <li>ADCS<br/>DACS<br/>IO<br/>Memory<br/>Platforms<br/>Utilities</li> <li>DSP System Toolbox</li> <li>DSP System Toolbox HDL Support</li> <li>HDL Coder</li> <li>Simulink 3D Animation</li> <li>Simulink Coder</li> <li>Simulink Extras<br/>Stateflow</li> <li>Xilinx Blockset</li> <li>Xilinx Reference Blockset<br/>Recently Used</li> </ul> | ADCs<br>IO<br>IO<br>Platforms | DACs   DACs   Memory   Utilities | sper_xps_s |

| 😣 🗖 🔲 Simulink Library Browser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        | _    |       |        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-------|--------|

| ← ⇒ Enter search term <ul> <li>▲ ▼</li> <li>■ ▼</li> <li>■ </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |      |       |        |

| CASPER XPS Blockset/Platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |      |       |        |

| <ul> <li>Simulink         Commonly Used Blocks         Continuous         Dashboard         Discontinuities         Discrete         Logic and Bit Operations         Lookup Tables         Math Operations         Model Verification         Model-Wide Utilities         Ports &amp; Subsystems         Signal Attributes         Signal Routing         Sinks         Sources         User-Defined Functions         Additional Math &amp; Discrete         Aerospace Blockset         Audio System Toolbox         CASPER DSP Blockset         ADCs         DACs         IO         Memory         Platforms         Utilities         Utilities         </li> </ul> | SKARAB | SNAP | SNAP2 | VCU118 |

casper\_xps\_select

Double click on the platform block that you just added. The Hardware Platform parameter should match the platform you are compiling for. Once you have selected a board, you need to choose where it will get its clock. In designs including ADCs you probably want the FPGA clock to be derived from the sampling clock, but for this simple design (which doesn't include an ADC) you should use the platform's on-board clock. To do this, set the User IP Clock Source to sys\_clk. The sys\_clk rate is 100 MHz, so you should set this for *User IP Clock Rate* in the block.

The configuration yellow block knows what FPGA corresponds to which platform, and so it will autmoatically configure the System Generator block which you previously added.

#### The System Generator and XPS Config blocks are required by all CASPER designs

## **Flashing LED**

To demonstrate the basic use of hardware interfaces, we will make an LED flash. With the FPGA running at ~100MHz (or greater), the most significant bit (msb) of a 27 bit counter will toggle approximately every 0.67 seconds. We can output this bit to an LED on your board. Most (all?) CASPER platforms have at least four LEDs, with the exact configuration depending on the board. We will make a small circuit connecting the top bit of a 27 bit counter to one of these LEDs. When compiled this will make the LED flash with a 50% duty cycle approximately once a second.

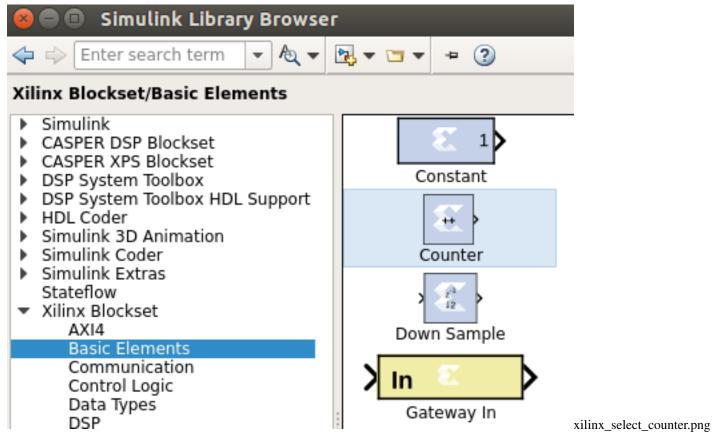

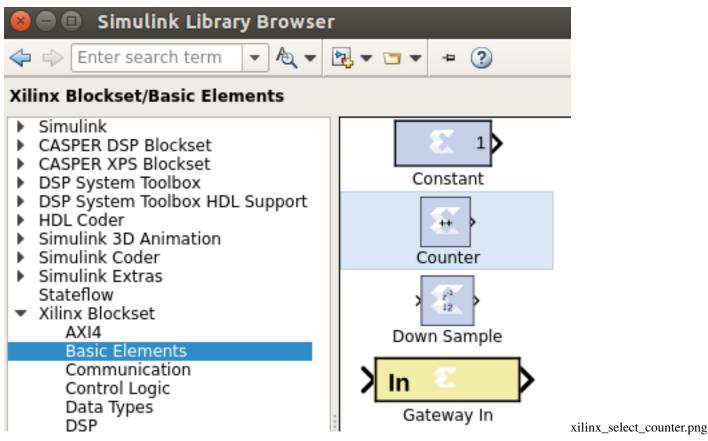

## Add a counter

Add a counter to your design by navigating to Xilinx Blockset -> Basic Elements -> Counter and dragging it onto your model.

Double-click it and set it for free running, 27 bits, unsigned. This means it will count from 0 to  $2^{27}$  - 1, and will then wrap back to zero and continue.

| 😣 🖨 🗊 count                                 | er_led (Xilinx Coun                                                              | iter)         |                          |

|---------------------------------------------|----------------------------------------------------------------------------------|---------------|--------------------------|

| least expensive in                          | Free running counters<br>n hardware. A count lir<br>nented by combining a<br>or. | nited         |                          |

| Basic Imple                                 | mentation                                                                        |               |                          |

| Counter type:                               | g 🔿 Count limited                                                                |               |                          |

| Count to value                              | Inf                                                                              |               |                          |

| Count direction:<br>● Up ○ Dow              | n 🔿 Up/Down                                                                      |               |                          |

| Initial value                               | 0                                                                                |               |                          |

| Step                                        | 1                                                                                |               |                          |

| Output Precisio                             | on ————                                                                          |               |                          |

| Output type:<br>Signed (2<br>Number of bits | ''s comp)   Unsigned                                                             | t l           |                          |

| Binary point                                | 0                                                                                |               |                          |

| -Optional Ports                             |                                                                                  |               |                          |

| 🗌 Provide load                              | port                                                                             |               |                          |

| 🗌 Provide synd                              | hronous reset port:                                                              |               |                          |

| Provide enal                                | ble port                                                                         |               |                          |

| Explicit Sample                             | e Period                                                                         |               |                          |

| Sample period                               |                                                                                  |               |                          |

| Explicit period                             | 1                                                                                |               |                          |

| 1.1. Vivado                                 |                                                                                  |               |                          |

| <u>o</u> k <u>c</u>                         | ancel <u>H</u> elp                                                               | <u>A</u> pply | xilinx_params_counter_le |

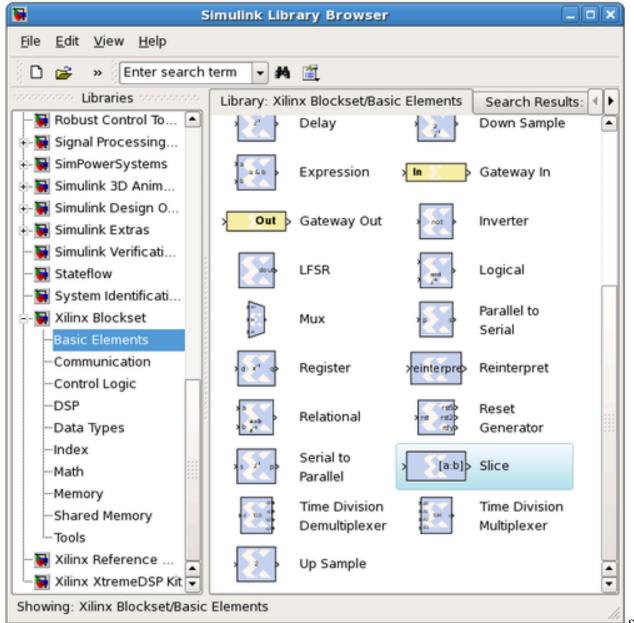

#### Add a slice block to select out the msb

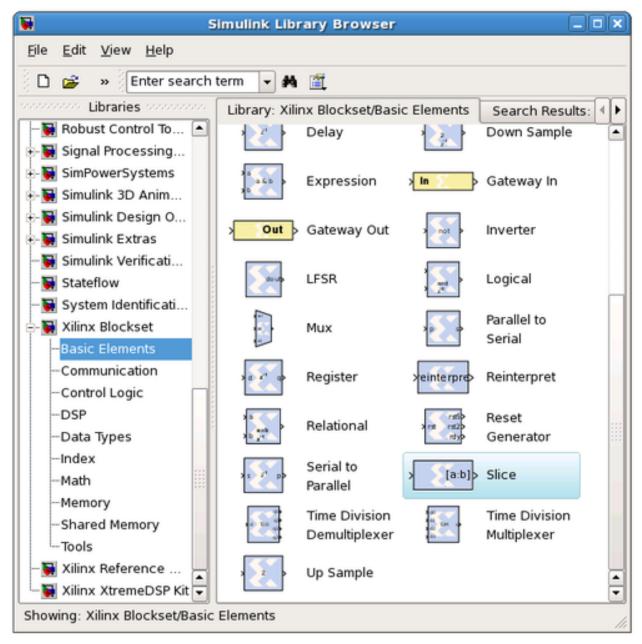

We now need to select the most significant bit (msb) of the counter. We do this using a slice block, which Xilinx provides. Xilinx Blockset -> Basic Elements -> Slice.

Slice\_select.png

Double-click on the newly added slice block. There are multiple ways to select which bit(s) you want. In this case, it is simplest to index from the upper end and select the first bit. If you wanted the least significant bit (lsb), you can also index from that position. You can either select the width and offset, or two bit locations.

Set it for 1 bit wide with offset from top bit at zero. As you might guess, this will take the 27-bit input signal, and output just the top bit.

| Slice (Xilinx Bit Slice Extractor)                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Extracts a given range of bits from each input sample and presents it at the output.<br>The output type is ordinarily unsigned with binary point at zero, but can be Boolean<br>when the slice is one bit wide.<br>Hardware notes: In hardware this block costs nothing. |

| Basic Advanced                                                                                                                                                                                                                                                           |

| Width of slice (number of bits) 1                                                                                                                                                                                                                                        |

| Boolean output                                                                                                                                                                                                                                                           |

| Specify range as:<br>Two bit locations Opper bit location + width Lower bit location + width                                                                                                                                                                             |

| Offset of top bit 0                                                                                                                                                                                                                                                      |

| Relative to:<br>OLSB of input OBinary point of input OBIN MSB of input                                                                                                                                                                                                   |

| Offset of bottom bit 0                                                                                                                                                                                                                                                   |

| Relative to:                                                                                                                                                                                                                                                             |

| <u>OK</u> <u>Cancel</u> <u>H</u> elp <u>A</u> pply                                                                                                                                                                                                                       |

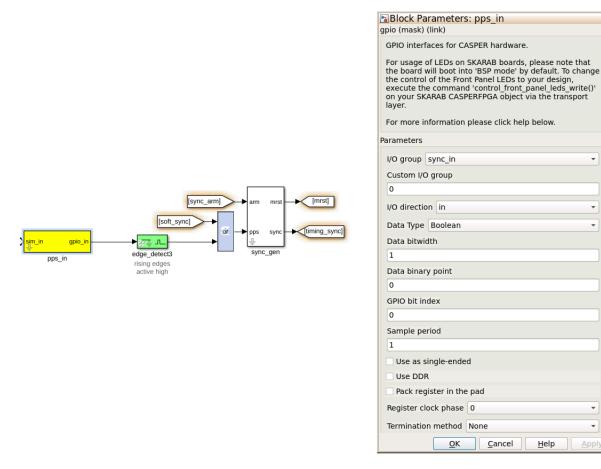

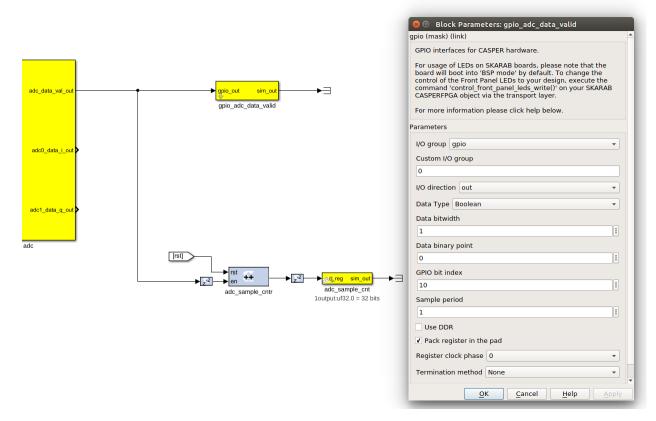

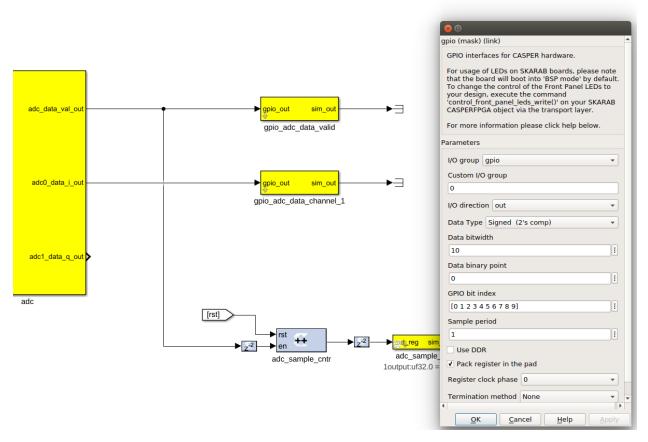

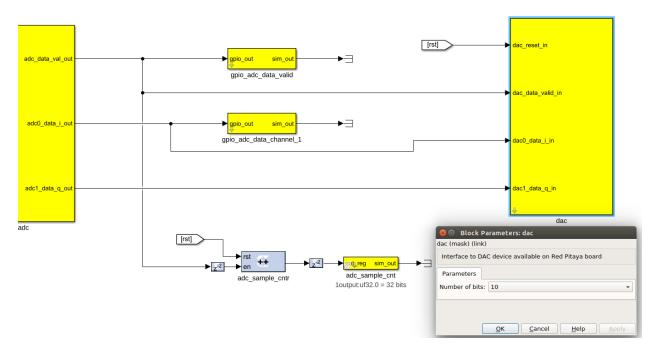

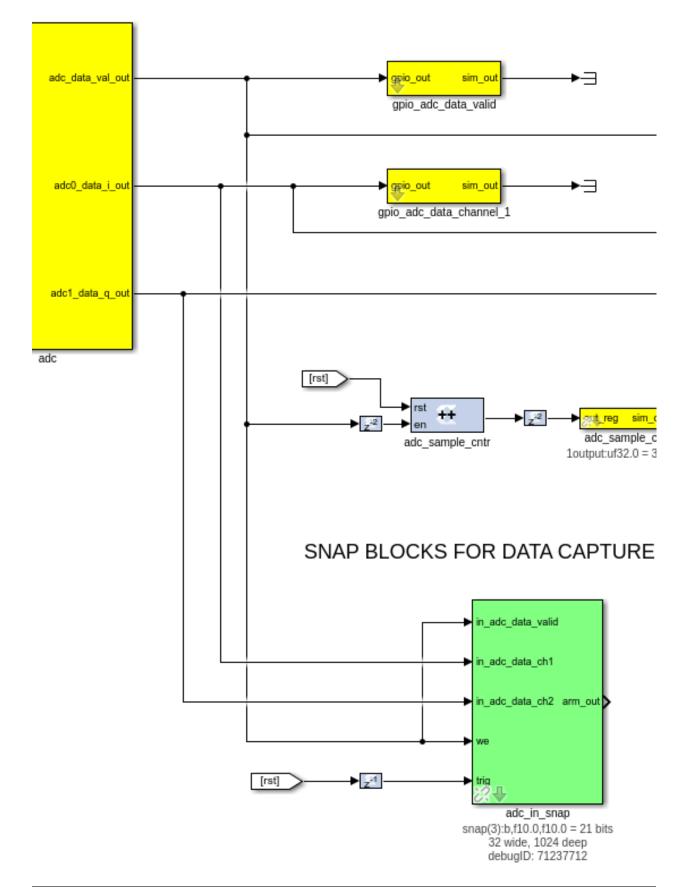

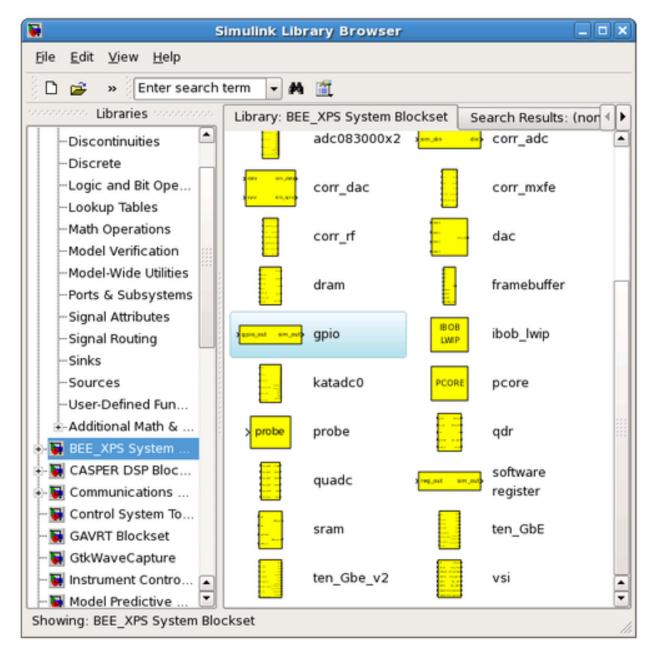

## Add a GPIO block

From: CASPER XPS library -> IO -> gpio.

In order to send the 1 bit signal you have sliced off to an LED, you need to connect it to the right FPGA output pin. To do this you can use a GPIO (general-purpose input/output) block from the XPS library, this allows you to route a signal from Simulink to a selection of FPGA pins, which are addressed with user-friendly names. Set it to use SNAP's LED bank as output. Once you've chosen the LED bank, you need to pick *which* LED you want to output to. Set the

GPIO bit index to 0 (the first LED) and the data type to Boolean with bitwidth 1. This means your simulink input is a 1 bit Boolean, and the output is LED0.

## 😣 🗉 🛛 Block Parameters: gpio

gpio (mask) (link)

GPIO interfaces for CASPER hardware.

For usage of LEDs on SKARAB boards, please note that the board will boot into 'BSP mode' by default. To change the control of the Front Panel LEDs to your design, execute the command 'control\_front\_panel\_leds\_write()' on your SKARAB CASPERFPGA object via the transport layer.

For more information please click help below.

| Parameters                                                |

|-----------------------------------------------------------|

| I/O group led 🔹                                           |

| Custom I/O group                                          |

| 0                                                         |

| I/O direction out                                         |

| Data Type Boolean 🔹                                       |

| Data bitwidth                                             |

| 1                                                         |

| Data binary point                                         |

| 0                                                         |

| GPIO bit index                                            |

| 0                                                         |

| Sample period                                             |

| 1                                                         |

| Use DDR                                                   |

| ✓ Pack register in the pad                                |

| 4 Register clock phase 0 Chapter 1. Tutorial Instructions |

| Termination method None                                   |

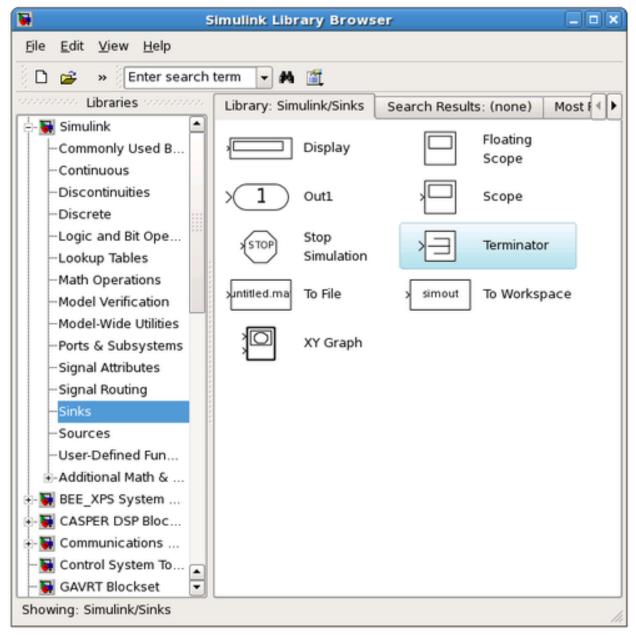

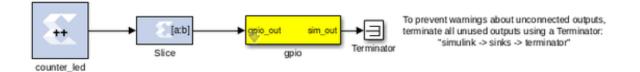

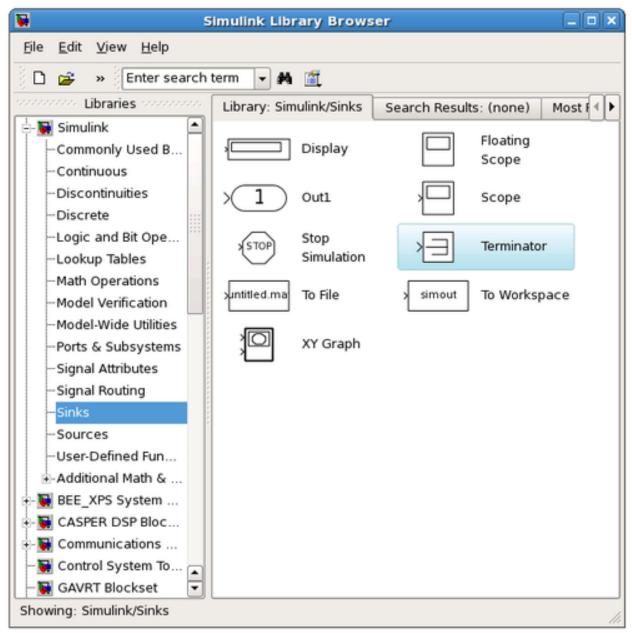

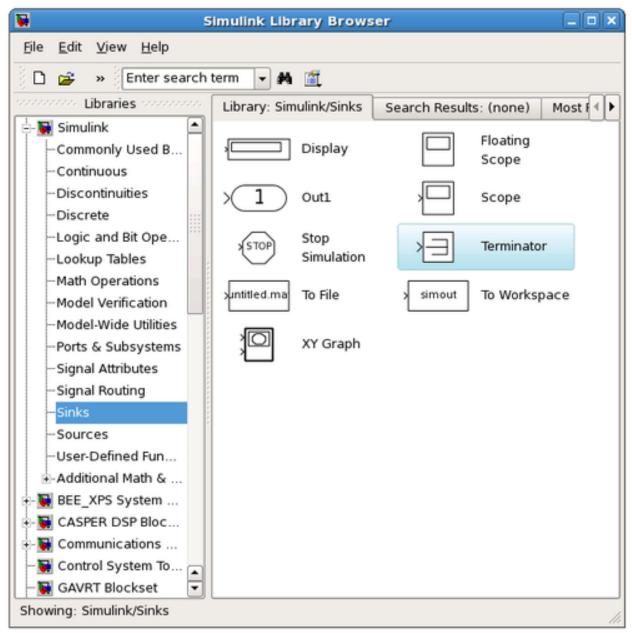

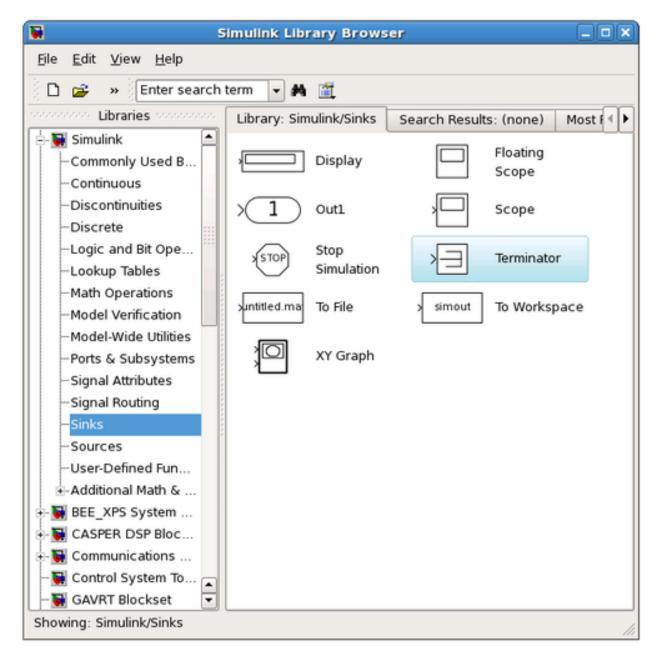

## Add a terminator

To prevent warnings (from MATLAB & Simulink) about unconnected outputs, terminate all unused outputs using a *Terminator*:

From: Simulink -> Sinks -> Terminator

You can also use the Matlab function XlAddTerms, run in the MATLAB prompt, to automatically terminate your unused outputs.

## Connect your design

It is a good idea to rename your blocks to something more sensible, like counter\_led instead of just counter. Do this simply by double-clicking on the name of the block and editing the text appropriately.

To connect the blocks simply click and drag from the 'output arrow' on one block and drag it to the 'input arrow' of another block. Connect the blocks together: Counter -> Slice -> gpio as showing in digram below.

Remember to save your design often.

#### Software control

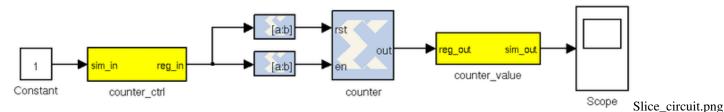

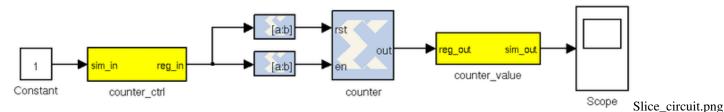

To demonstrate the use of software registers to control the FPGA from a computer, we will add a registers so that the counter in our design can be started, stopped, and reset from software. We will also add a register so that we can monitor the counter's current value too.

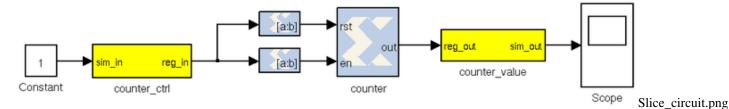

By the end of this section, you will create a system that looks like this:

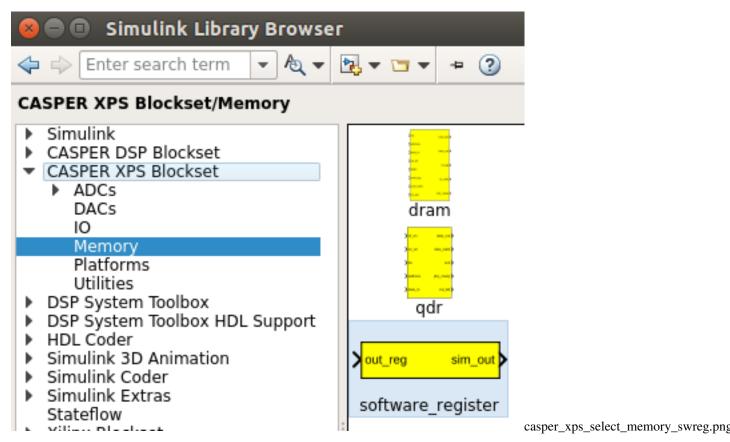

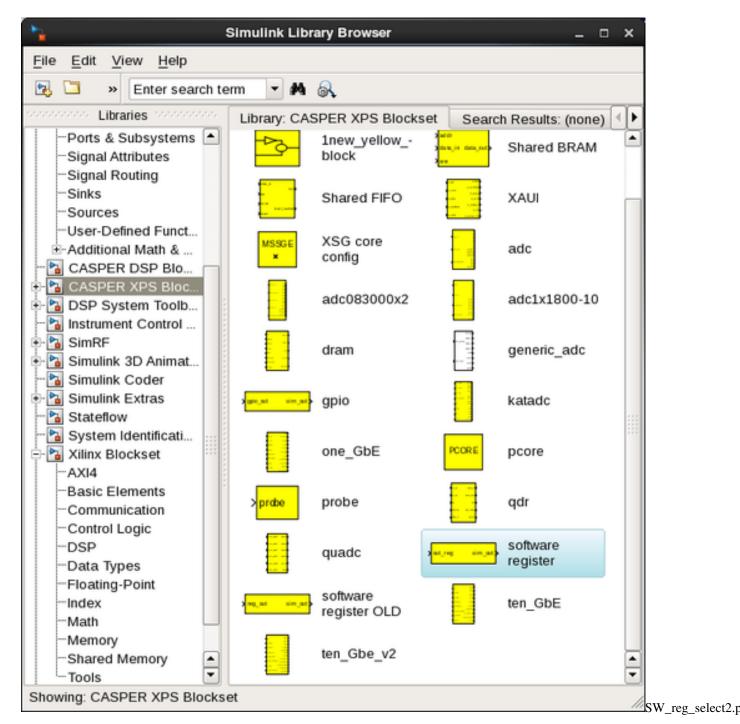

#### Add the software registers

We need two software registers. One to control the counter, and a second one to read its current value. From the CASPER XPS System Blockset library, drag two Software Registers onto your design.

Set the I/O direction to *From Processor* on the first one (counter control) to enable a value to be set from software and sent *to* your FPGA design. Set it to *To Processor* on the second one (counter value) to enable a value to be sent *from* the FPGA to software. Set both registers to a bitwidth of 32 bits.

# 😣 💿 🛛 Block Parameters: counter\_ctrl

## swreg (mask)

A 32-bit software-accessible register. Can be divided into bitfields of varying widths and types using the fields in the block mask.

| Setup                                |                                 |

|--------------------------------------|---------------------------------|

| I/O direction From Processor         | •                               |

| I/O delay                            |                                 |

| 0                                    |                                 |

| Initial Value                        |                                 |

| 0                                    |                                 |

| Sample period                        |                                 |

| 1                                    |                                 |

| Bitfield names [msblsb]              |                                 |

| reg                                  |                                 |

| Bitfield widths                      |                                 |

| 32                                   |                                 |

| Bitfield binary pts                  |                                 |

| 0                                    |                                 |

| Bitfield types, ufix=0, fix=1, bool= | 2                               |

| 0                                    |                                 |

| Provide sim input/output?            | Chapter 1. Tutorial Instruction |

| Print format string?                 |                                 |

|                                      |                                 |

# 😣 🗊 🛛 Block Parameters: counter\_value

swreg (mask)

A 32-bit software-accessible register. Can be divided into bitfields of varying widths and types using the fields in the block mask.

| Setup                                 |

|---------------------------------------|

| I/O direction To Processor            |

| I/O delay                             |

| 0                                     |

| Initial Value                         |

| 0                                     |

| Sample period                         |

| 1                                     |

| Bitfield names [msblsb]               |

| reg                                   |

| Bitfield widths                       |

| 32                                    |

| Bitfield binary pts                   |

| 0                                     |

| Bitfield types, ufix=0, fix=1, bool=2 |

Rename the registers to something sensible. The names you give them here are the names you will use to access them from software. Do not use spaces, slashes and other funny characters in these. Perhaps *counter\_ctrl* and *counter\_value*, to represent the control and output registers respectively.

Also note that the software registers have *sim\_reg* and *sim\_out* ports. The input port provides a means of simulating this register's value (as would be set by the runtime software) using the sim\_reg line. The output port provides a means to simulate this register's current FPGA-assigned value.

For now, set the sim\_reg port to constant one using a Simulink-type constant. Found in *Simulink -> Sources*. This will enable the counter during simulations.

| <u>Eile E</u> dit <u>V</u> iew <u>H</u> elp        |                          |                              |                       |                               |    |

|----------------------------------------------------|--------------------------|------------------------------|-----------------------|-------------------------------|----|

| 🗅 😅 🔹 Enter search                                 | term 👻 🎮                 | <b>1</b>                     |                       |                               |    |

| Constants Libraries Constants                      | Library: Sim             | ulink/Sources                | Search Res            | ults: (none)                  | Mo |

| Commonly Used B                                    | լլե                      | Band-Limited<br>White Noise  | ~\W}>                 | Chirp Signal                  |    |

| Discontinuities<br>Discrete                        |                          | Clock                        | 1                     | Constant                      |    |

| Logic and Bit Ope<br>Lookup Tables                 | $\mathcal{A}\mathcal{A}$ | Counter Free-<br>Running     | [] <b>??</b> ]/>      | Counter<br>Limited            |    |

| Math Operations<br>Model Verification              | 12:34                    | Digital Clock                | SiDem e Sign Positive | Enumerated<br>Constant        |    |

| Model-Wide Utilities<br>Ports & Subsystems         | untitled.mat             | From File                    | simin                 | From<br>Workspace             |    |

| – Signal Attributes<br>– Signal Routing<br>– Sinks | F                        | Ground                       |                       | In1                           |    |

| - <mark>Sources</mark><br>User-Defined Fun         | ///}                     | Pulse<br>Generator           |                       | Ramp                          |    |

| • Additional Math &<br>• 🙀 BEE_XPS System          | M                        | Random<br>Number             | M                     | Repeating<br>Sequence         |    |

| CASPER DSP Bloc                                    | $\land$                  | Repeating Se-<br>quence Inte | հՆ                    | Repeating Se-<br>quence Stair |    |

| 🙀 Control System To 🔺<br>🙀 GAVRT Blockset 🛛 🔻      | Signal 1                 | Signal Builder               |                       | Signal                        |    |

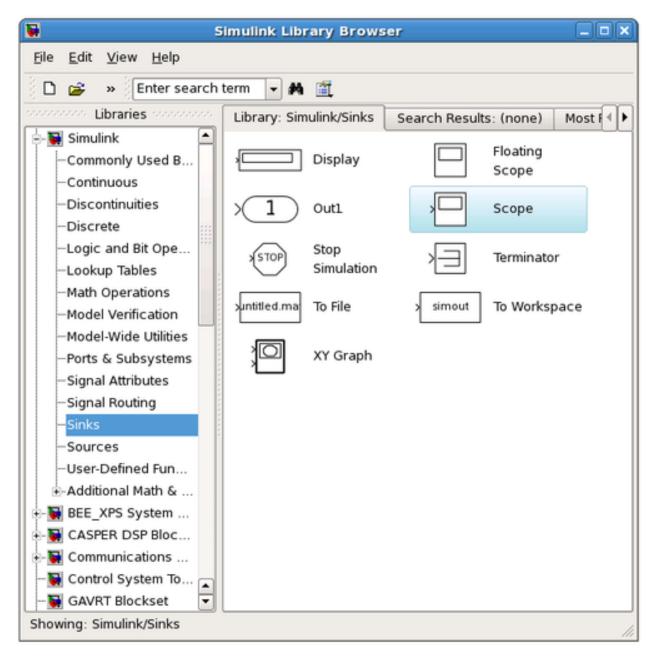

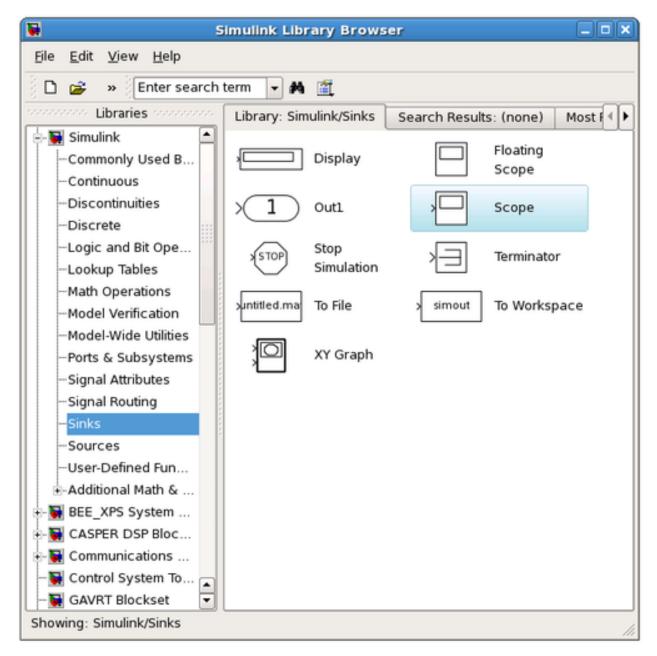

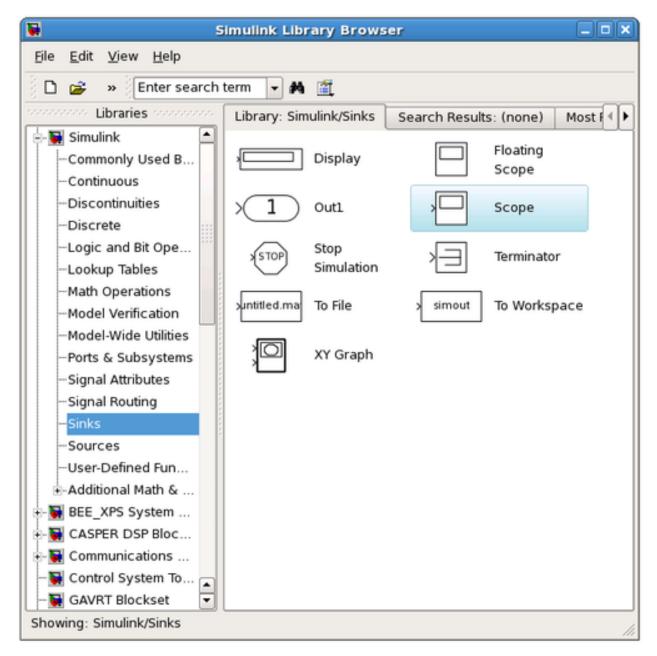

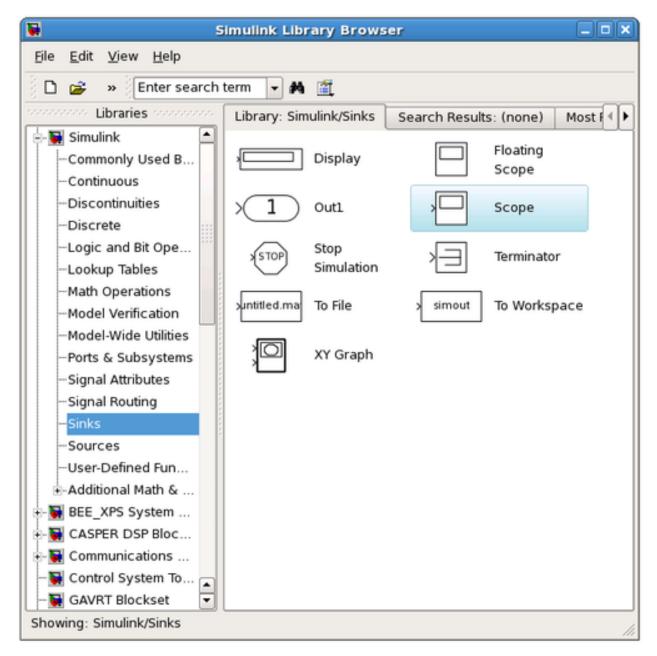

During simulation, we can monitor the counter's value using a scope (*Simulink -> Sinks*):

Here is a good point to note that all blocks from the *Simulink* library (usually white), will not be compiled into hardware. They are present for simulation only.

Only Xilinx blocks (they are blue with Xilinx logo) will be compiled to hardware.

You need to use *gateway* blocks whenever connecting a Simulink-provided block (like a scope or sine-wave generator) to a from a Xilinx block, this will sample and quantize the simulink signals so that they are compatible with the Xilinx world. Some blocks (like the software register) provide a gateway internally, so you can feed the input of a software register with a xilinx signal, and monitor its output with a Simulink scope. However, in general, you must manually insert these gateways where appropriate. Simulink will issue warnings for any direct connections between the Simulink and Xilinx worlds.

## Add the counter

You can do this either by copying your existing counter block (copy-paste, or ctrl-click-drag-drop) or by placing a new one from the library.

Configure it with a reset and enable port as follows:

| ) (                     | counter (Xilinx Counter)                                                                           |     |

|-------------------------|----------------------------------------------------------------------------------------------------|-----|

|                         | s: Free running counters are the least e<br>unt limited counter is implemented by o<br>comparator. |     |

| Basic Adva              | nced Implementation                                                                                |     |

| Counter type:           | ng OCount limited                                                                                  |     |

| Count to value          | Inf                                                                                                |     |

| Count direction         | 1:                                                                                                 |     |

| ⊛Up ⊖Do                 | wn OUp/Down                                                                                        |     |

| Initial value           | 0                                                                                                  |     |

| Step                    | 1                                                                                                  |     |

| Output Precis           | ion                                                                                                |     |

| Output type:<br>Osigned | (2's comp)                                                                                         |     |

| Number of bit           | ts 32                                                                                              |     |

| Binary point            | 0                                                                                                  |     |

| Optional Ports          | 5                                                                                                  |     |

| Provide loa             |                                                                                                    |     |

| ✓ Provide sy            | nchronous reset port                                                                               |     |

| ✓ Provide en            | able port                                                                                          |     |

| Explicit Samp           | le Period                                                                                          |     |

| Sample perio            | d source:                                                                                          |     |

| Explicit                | O Inferred from inputs                                                                             |     |

| Explicit period         | d 1                                                                                                |     |

|                         |                                                                                                    |     |

|                         |                                                                                                    |     |

| Vivado                  |                                                                                                    |     |

| <u>O</u> K              | <u>Cancel H</u> elp <u>Ap</u>                                                                      | ply |

|                         |                                                                                                    |     |

#### Add the slice blocks

Now we need some way to control the enable and reset ports of the counter. We could do this using two separate software registers, but this is wasteful since each register is 32 bits anyway.

So we'll use a single register and slice out one bit for enabling the counter, and another bit for resetting it. Either copy your existing slice block (copy-paste it or hold ctrl while dragging/dropping it) or add two more from the library.

The enable and reset ports of the counter require boolean values (which Simulink interprets differently from ordinary 1-bit unsigned numbers). Configure the slices as follows:

Slice for enable:

| 😕 亘 💿 slice_enable (Xilinx Bit Slice Extractor)                                                                                                                                                                 |               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Extracts a given range of bits from each input sample and presents it at the output.<br>The output type is ordinarily unsigned with binary point at zero, but can be Boolean<br>when the slice is one bit wide. |               |

| Hardware notes: In hardware this block costs nothing.                                                                                                                                                           |               |

| Basic                                                                                                                                                                                                           |               |

| Width of slice (number of bits) 1                                                                                                                                                                               |               |

| Boolean output                                                                                                                                                                                                  |               |

| Specify range as:<br>O Two bit locations O Upper bit location + width O Lower bit location + width                                                                                                              |               |

| Offset of top bit 0                                                                                                                                                                                             |               |

| Relative to:                                                                                                                                                                                                    |               |

| ○ LSB of input ○ Binary point of input ◎ MSB of input                                                                                                                                                           |               |

| Offset of bottom bit 0                                                                                                                                                                                          |               |

| <ul> <li>Relative to:</li> <li>LSB of input</li> <li>Binary point of input</li> <li>MSB of input</li> </ul>                                                                                                     |               |

|                                                                                                                                                                                                                 |               |

| <u>O</u> K <u>Cancel H</u> elp <u>A</u> pply                                                                                                                                                                    | casper_xps_pa |

Slice for reset:

| 😵 🗇 💿 🛛 slice_reset (Xilinx Bit Slice Extractor)                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Extracts a given range of bits from each input sample and presents it at the output.<br>The output type is ordinarily unsigned with binary point at zero, but can be Boolean<br>when the slice is one bit wide. |

| Hardware notes: In hardware this block costs nothing.                                                                                                                                                           |

| Basic                                                                                                                                                                                                           |

| Width of slice (number of bits) 1                                                                                                                                                                               |

| 🗱 Boolean output                                                                                                                                                                                                |

| Specify range as:<br>O Two bit locations O Upper bit location + width O Lower bit location + width                                                                                                              |

| Offset of top bit 0                                                                                                                                                                                             |

| Relative to:<br>O LSB of input O Binary point of input O MSB of input                                                                                                                                           |

| Offset of bottom bit 1                                                                                                                                                                                          |

| Relative to:                                                                                                                                                                                                    |

|                                                                                                                                                                                                                 |

| OK Cancel Help Apply                                                                                                                                                                                            |

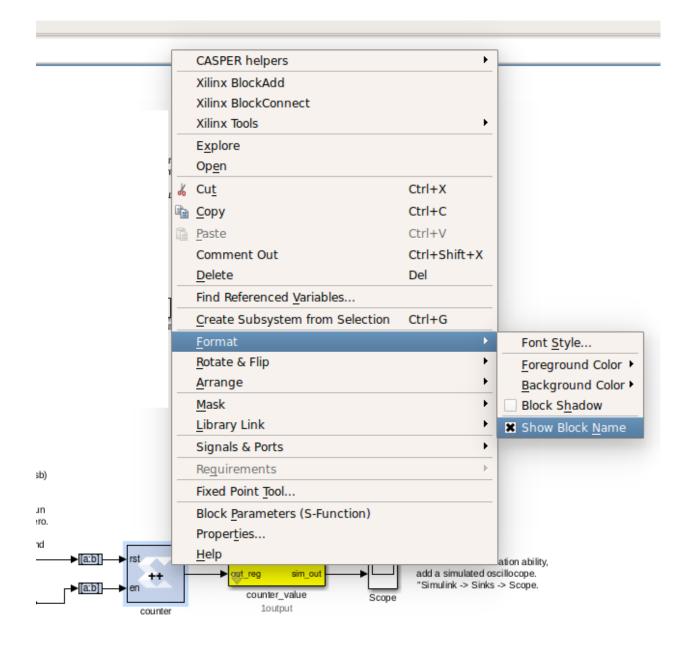

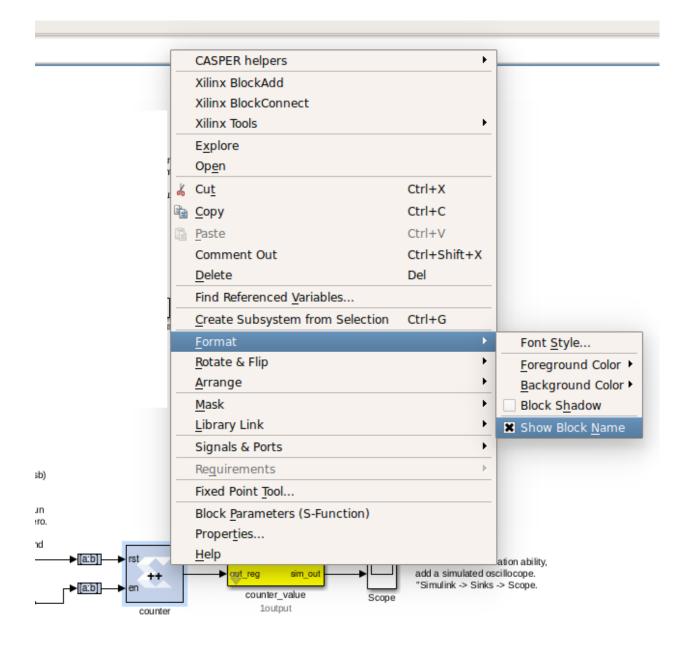

## Connect it all up

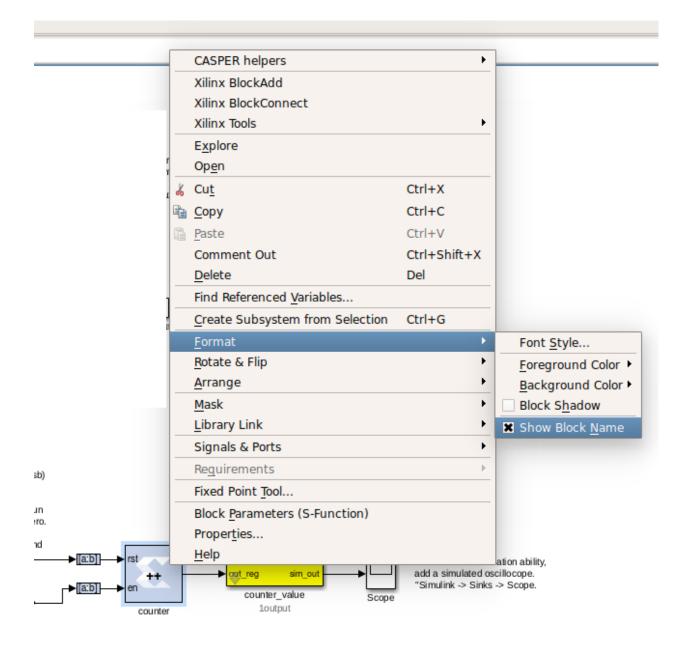

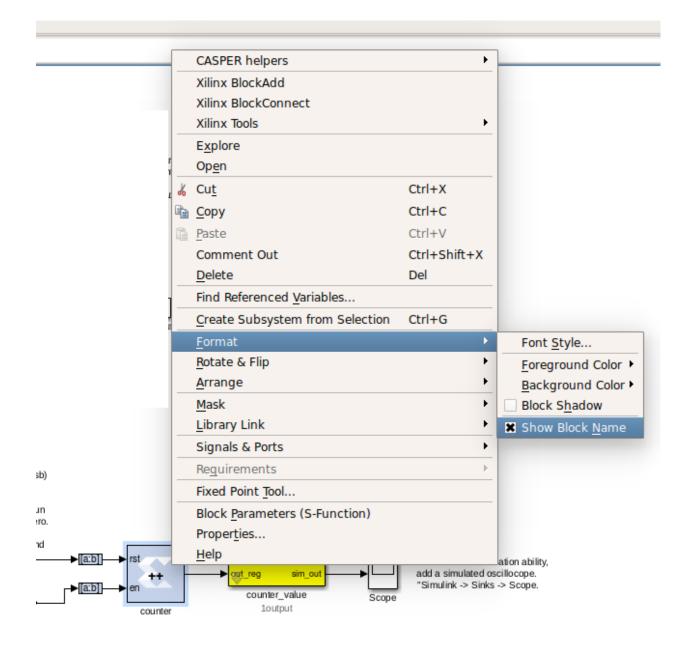

Now we need to connect all these blocks together. To neaten things up, consider resizing the slice blocks and hiding their names. Their function is clear enough from their icon without needing to see their names.

Do so by right-clicking and unchecking Format  $\rightarrow$  Show Block Name. You could do this with the counter too, but it's not a good idea with the software registers, because otherwise you wouldn't know how to address them when looking at your diagram.

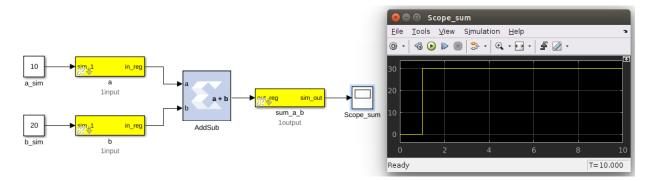

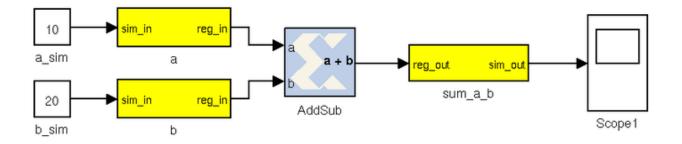

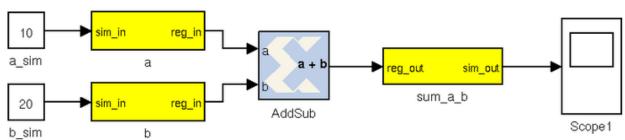

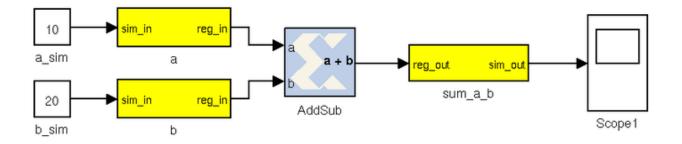

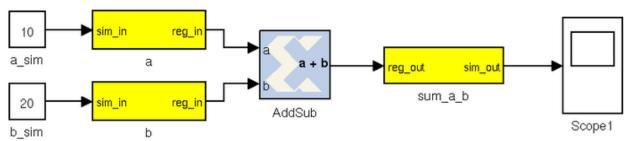

## Adder

To demonstrate some simple mathematical operations, we will create an adder. It will add two numbers on demand and output the result to another software register. Almost all astronomy DSP is done using fixed-point (integer) notation, and this adder will be no different.

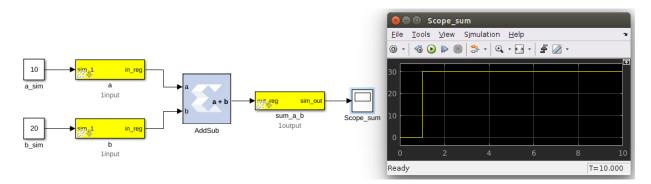

We will calculate  $a+b = sum\_a\_b$ .

## Add the software registers

Add two more input software registers. These will allow us to specify the two numbers to add. Add another output register for the sum output.

Either copy your existing software register blocks (copy-paste or holding ctrl while dragging/dropping it) or add three more from the library. Set the I/O direction to From Processor on the first two and set it to To Processor on the third one.

#### Add the adder block

Locate the adder/subtractor block, Xilinx Blockset -> Math -> AddSub and drag one onto your design. This block can optionally perform addition or subtraction. Let's leave it set at it's default, for addition.

| 🛚 🗖 🔲 AddSub (Xilinx Adder/Subtracter)                                                 |            |                |              |       |   |

|----------------------------------------------------------------------------------------|------------|----------------|--------------|-------|---|

| Basic Output Implementation                                                            |            |                |              |       |   |

| Operation:<br>Addition      Subtraction      Addition or subtraction<br>Optional Ports |            |                |              |       |   |

| Provide carry-in port                                                                  |            |                |              |       |   |

| Provide carry-out port                                                                 |            |                |              |       |   |

| Provide enable port                                                                    |            |                |              |       |   |

| Latency 0                                                                              |            |                |              |       |   |

|                                                                                        |            |                |              |       |   |

|                                                                                        |            |                |              |       |   |

|                                                                                        | <u>о</u> к | <u>C</u> ancel | <u>H</u> elp | Apply | _ |

The output register is 32 bits. If we add two 32 bit numbers, we will have 33 bits.

There are a number of ways of fixing this:

- limit the input bitwidth(s) with slice blocks

- limit the output bitwidth with slice blocks

- create a 32 bit adder.

Since you have already seen slice blocks demonstrated, let's try to set the AddSub block to be a 32 bit saturating adder. On the second tab, set it for user-defined precision, unsigned 32 bits.

Also, under overflow, set it to saturate. Now if we add two very large numbers, it will simply return 2^32 -1.

| 😣 🖃 🔲 AddSub (Xilinx Adder/Subtracter)                                                                                                                                 |            |                   |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|--|--|--|

| Basic                                                                                                                                                                  | Output     | Implementation    |  |  |  |

| Precision:<br>) Full  User defined<br>Fixed-point Output Type                                                                                                          |            |                   |  |  |  |

| Arithmetic type:<br>Signed (2's comp)  Unsigned<br>Fixed-point Precision<br>Number of bits 32 Binary point 0                                                           |            |                   |  |  |  |

| Quantization:<br><ul> <li>Truncate</li> <li>Round (unbiased: +/- Inf)</li> </ul> <li>Overflow: <ul> <li>Wrap</li> <li>Saturate</li> <li>Flag as error</li> </ul> </li> |            |                   |  |  |  |

|                                                                                                                                                                        | <u>о</u> к | Cancel Help Apply |  |  |  |

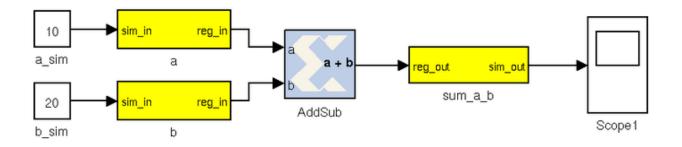

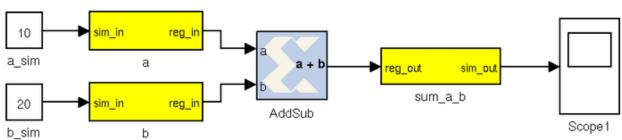

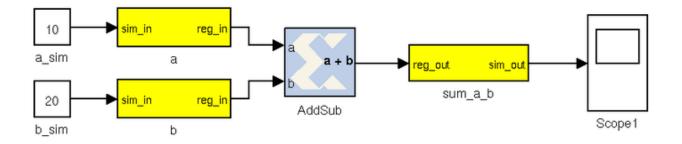

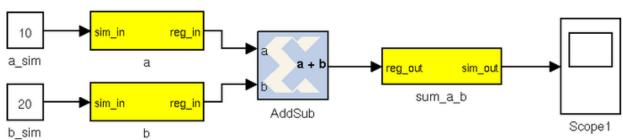

## Add the scope and simulation inputs

Either copy your existing scope and simulation constants (copy-paste or ctrl-drag) or place a new one from the library as before. Set the values of the simulation inputs to anything you like.

## **Connect it all together**

Like this:

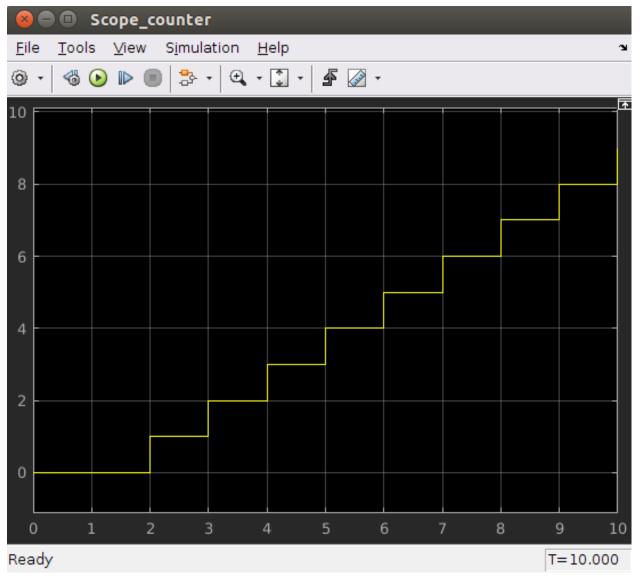

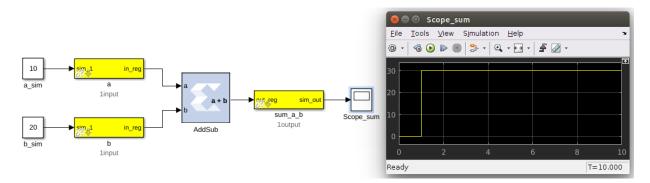

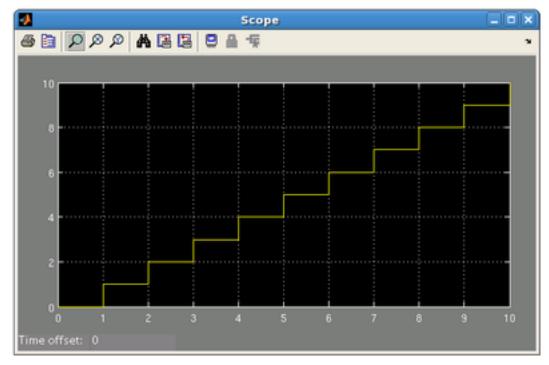

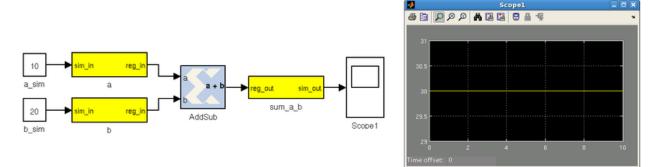

## Simulating

The design can be simulated with clock-for-clock accuracy directly from within Simulink. Set the number of clock cycles that you'd like to simulate and press the play button in the top toolbar.

| Τ |     | _ |  |   |    |          |   |

|---|-----|---|--|---|----|----------|---|

|   | - 🖑 |   |  | • | 10 | Normal 🔻 | • |

|   |     |   |  |   |    |          | _ |

You can watch the simulation progress in the status bar in the bottom right. It will complete in the blink of an eye for this small design with just 10 clock cycles.

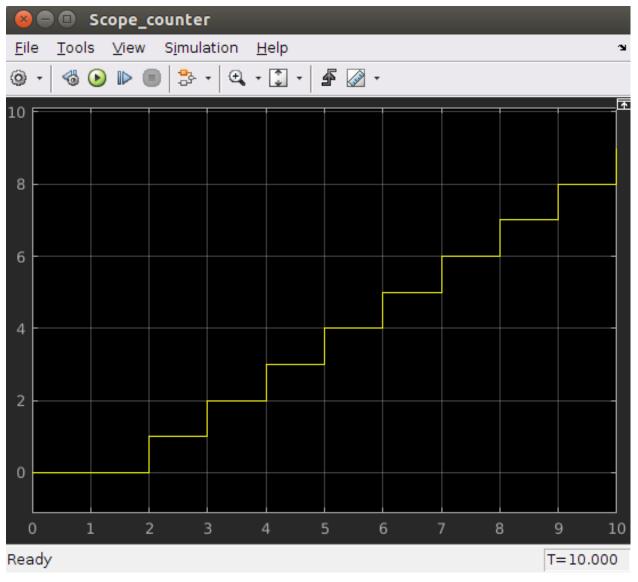

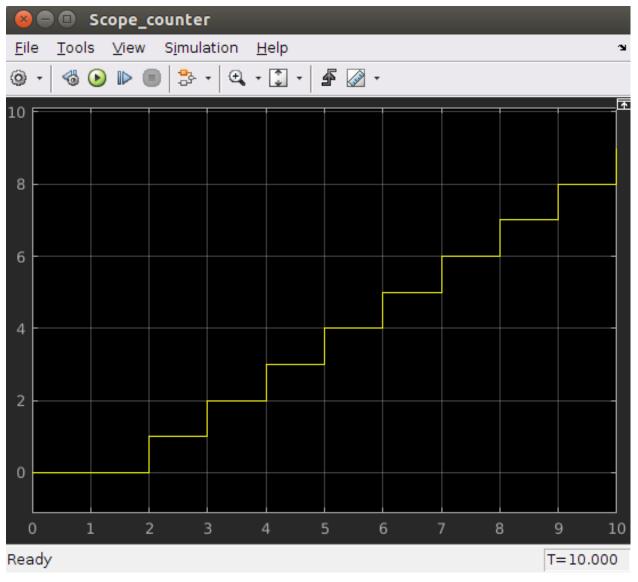

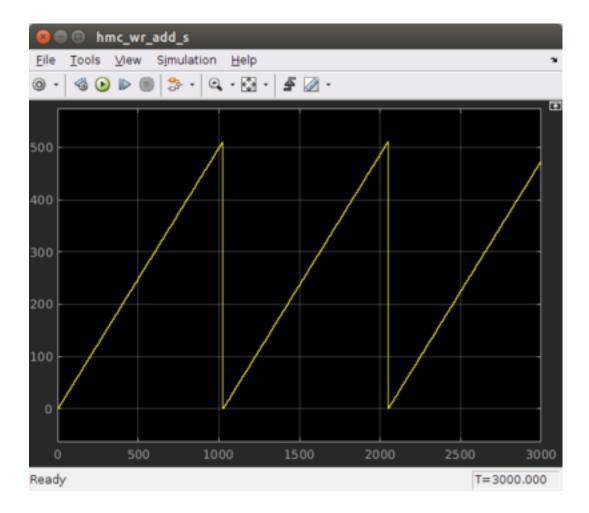

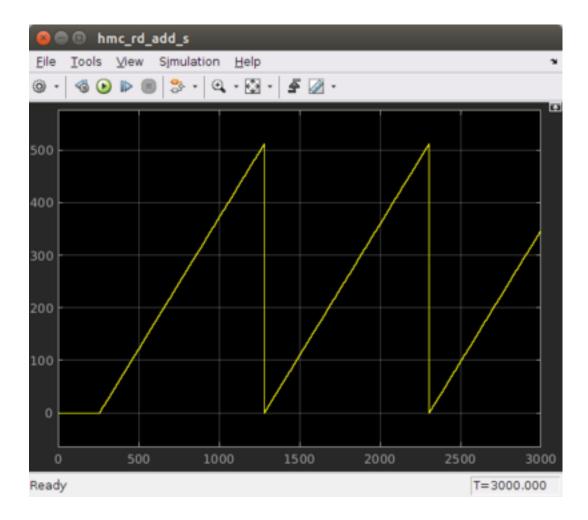

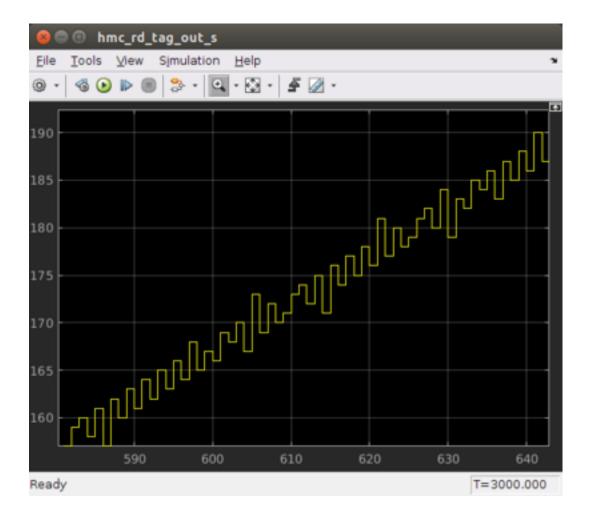

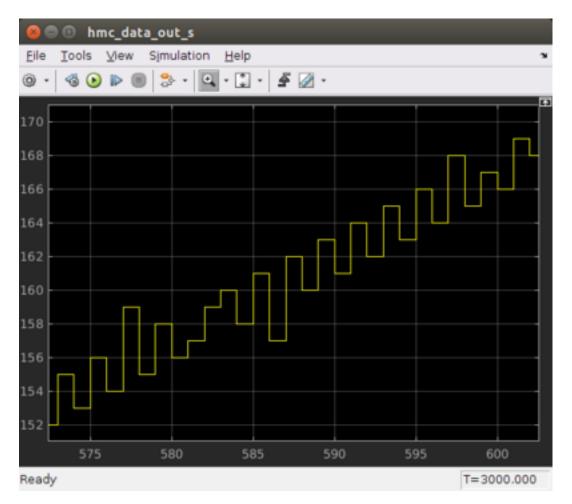

You can double-click on the scopes to see what the signals look like on those lines. For example, the one connected to the counter should look like this:

The one connected to your adder should return a constant, equal to the sum of the two numbers you entered. You might have to press the Autoscale button to scale the scope appropriately.

Once you have verified that that design functions as you'd like, you're ready to compile for the FPGA...

#### Compiling

Essentially, you have constructed three completely separate little instruments. You have a flashing LED, a counter which you can start/stop/reset from software and also an adder. These components are all clocked off the same 156.25MHz system clock crystal and to your specified User IP Clock Rate, but they will operate independently.

In order to compile this to an FPGA bitstream, execute the following command in the MATLAB Command Line window. THIS COMMAND DEPENDS WHICH PLATFORM YOU ARE TARGETING:

>> jasper

When a GUI pops up, click "Compile!". This will run the complete build process, which consists of two stages. The first involving Xilinx's System Generator, which compiles any Xilinx blocks in your Simulink design to a circuit which can be implemented on your FPGA. While System Generator is running, you should see the following window pop up:

| 😣 🔵 System Ge                       | enerator: snap_tut             |                 |                   |

|-------------------------------------|--------------------------------|-----------------|-------------------|

| Compilati Clocking General          |                                |                 |                   |

| Board :                             |                                | 800             | Compilation       |

| None                                |                                |                 |                   |

| Part :                              |                                | -               |                   |

| Kintex7 xc7k160t-2ffg676            |                                | General General | ting              |

| Compilation :                       |                                |                 |                   |

| HDL Netlist                         | Settings                       |                 |                   |

| Hardware description                | VHDL library :                 |                 |                   |

| VHDL                                | <pre>xil_defaultlib</pre>      | Ca              | ncel Show Details |

| Use STD_LOGIC type for Boolean of   |                                |                 |                   |

| Target directory                    |                                |                 |                   |

| /home/qwerty40/casper/tutorials_dev |                                |                 |                   |

| Synthesis strategy : In             | plementation strategy :        |                 |                   |

| Vivado Synthesis Defaults 📼 Viv     | vado Implementation De 🔻       |                 |                   |

| Create interface document           | Create testbench Model upgrade |                 |                   |

| Performance T Generate OK           | Apply Cancel Help              |                 |                   |

After this, the second stage involves synthesis of your design through Vivado, which goes about turning your design into a physical implementation and figuring out where to put the resulting components and signals on your FPGA. Finally the toolflow will create the final output fpg file that you will use to program your FPGA. This file contains the bitstream (the FPGA configuration information) as well as meta-data describing what registers and other yellow blocks are in your design. This file will be created in the 'outputs' folder in the working directory of your Simulink model. **Note: Compile time is approximately 15-20 minutes**.

```

amish@amish-desktop:~/Documents/tut_1$ cd tut_1/

myproj/ outputs/ sysgen/

amish@amish-desktop:~/Documents/tut_1$ cd tut_1/outputs/

amish@amish-desktop:~/Documents/tut_1/tut_1/outputs$ ls -lt

total 8336

-rw-rw-r-- 1 amish amish 1249412 Jul 25 14:18 tut_1_2017-7-25_1355.fpg

-rw-rw-r-- 1 amish amish 7280615 Jul 25 14:18 tut_1_2017-7-25_1355.bof

amish@amish-desktop:~/Documents/tut_1/tut_1/outputs$

```

## **Advanced Compiling**

Once you are familiar with the CASPER toolflow, you might find you want to run the two stages of the compile separately. This means that MATLAB will become usable sooner, since it won't be locked up by the second stage of the compile. If you want to do this, you can run the first stage of the compile from the MATLAB prompt with

>> jasper\_frontend

After this is completed, the last message printed will tell you how to finish the compile. It will look something like:

You can run this command in a separate terminal, after sourcing appropriate environment variables. Not recommended for beginners.

## **Programming the FPGA**

Reconfiguration of CASPER FPGA boards is achieved using the casperfpga python library, created by the SA-SKA group.

## Getting the required packages

These are pre-installed on the server in the workshop and you do not need to do any further configuration. However, should you want to run these tutorials on your own machines, you should download the latest casperfpga libraries from here.

## Copy your .fpg file to your Server

As per the previous figure, navigate to the outputs folder and (secure)copy this across to a test folder on the workshop server. Instructions to do this are available here

#### Connecting to the board

SSH into the server that the SNAP board is connected to and navigate to the folder in which your .fpg file is stored.

Start interactive python by running:

\$ ipython

Now import the fpga control library. This will automatically pull-in the KATCP library and any other required communications libraries.

import casperfpga

To connect to the board we create a CasperFpga instance; let's call it fpga. The CasperFpga constructor requires just one argument: the IP hostname or address of your FPGA board.

fpga = casperfpga.CasperFpga('SNAP hostname or ip\_address')

The first thing we do is program the FPGA with the .fpg file which your compile generated.

fpga.upload\_to\_ram\_and\_program('your\_fpgfile.fpg')

Should the execution of this command return true, you can safely assume the FPGA is now configured with your design. You should see the LED on your board flashing. Go check! All the available/configured registers can be displayed using:

fpga.listdev()

The adder and counter can be controlled by writing to and reading from registers added in the design using:

```

fpga.write_int('a',10)

fpga.write_int('b',20)

fpga.read_int('sum_a_b')

```

With any luck, the sum returned by the FPGA should be correct.

You can also try writing to the counter control registers in your design. You should find that with appropriate manipulation of the control register, you can make the counter start, stop, and return to zero.

```

fpga.write_int('counter_ctrl',10')

fpga.read_uint('counter_value')

```

#### Conclusion

This concludes the first CASPER Tutorial. You have learned how to construct a simple Simulink design, program an FPGA board and interact with it with Python using casperfpga. Congratulations!

While the design you made might not be very complicated, you now have the basic skills required to build more complex designs which are covered in later tutorials.

## 1.1.2 Tutorial 2: 10GbE Interface

## Introduction

In this tutorial, you will create a simple Simulink design which uses the SNAP's 10GbE ports to send data at high speeds to another port. This could just as easily be another FPGA board or a computer with a 10GbE network interface card. In addition, we will learn to control the design remotely, using a supplied Python library for KATCP.

In this tutorial, a counter will be transmitted through one SFP+ port and back into another. This will allow a test of the communications link. This test can be used to test the link between boards and the effect of different cable lengths on communication robustness.

## Background

SNAP boards have two on-board SFP+ ports. The Ethernet interface is driven by an on-board 156.25MHz crystal oscilator. This clock is then multiplied up on the FPGA by a factor of 66. Thus, the speed on the wire is actually 156.25MHz x 66 = 10.312.5 Gbps. However, 10GbE over single-lane SFP+ connectors uses 64b/66b encoding, which means that for every 66 bits sent, 66 bits are actually transmitted. This is to ensure proper clocking, since the receiver recovers and locks-on to the transmitter's clock and requires edges in the data. Imagine transmitting a string of 0xFF or 0b11111111... which would otherwise generate a DC level on the line, now an extra two bits are introduced which includes a zero bit which the receiver can use to recover the clock and byte endings. See here for more information.

For this reason, we actually get 10Gbps usable data rate. CASPER's 10GbE Simulink core sends and receives UDP over IPv4 packets. These IP packets are wrapped in Ethernet frames. Each Ethernet frame requires a 38 byte header, IPv4 requires another 20 bytes and UDP a further 16. So, for each packet of data you send, you will incur a cost of at least 74 bytes. I say at least, because the core will zero-pad some headers to be on a 64-bit boundary. You will thus never achieve 10Gbps of usable throughput, though you can get close. It pays to send larger packets if you are trying to get higher throughputs.

The maximum payload length of the CASPER 10GbE core is 8192 bytes (implemented in BRAM) plus another 512 (implemented in distributed RAM) which is useful for an application header. These ports (and hence part of the 10 GbE cores) run at 156.25MHz, while the interface to your design runs at the FPGA clock rate (sys\_clk, adcX\_clk etc). The interface is asynchronous, and buffers are required at the clock boundary. For this reason, even if you send data between two SNAP boards which are running off the same hard-wired clock, there will be jitter in the data. A second consideration is how often you clock values into the core when you try to send data. If your FPGA is running faster than the core, and you try and clock data in on every clock cycle, the buffers will eventually overflow. Likewise for receiving, if you send too much data to a board and cannot clock it out of the receive buffer fast enough, the receive buffers will overflow and you will lose data. In our design, we are clocking the FPGA at 100 MHz, with the cores running at 156.25MHz. We can thus clock data into the TX buffer continuously without worrying about overflows.

## Create a new model

Start Matlab and open Simulink (either by typing 'simulink' on the Matlab command line, or by clicking on the Simulink icon in the taskbar). A template is provided for Tut2 with a pre-created packet generator in the tutorials\_devel git repository. Get a copy of this template and save it. You will need the SNAP block in the Platforms subdirectory of the xps\_library. Specify a clock frequency of 100 MHz and the clock source "sys\_clock".

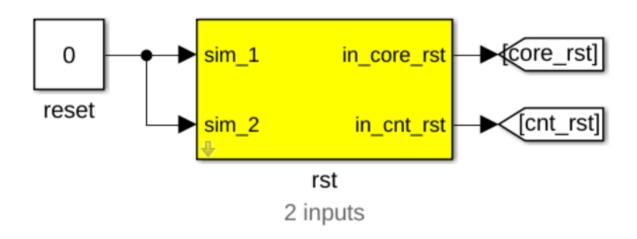

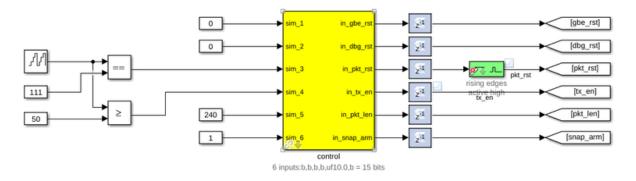

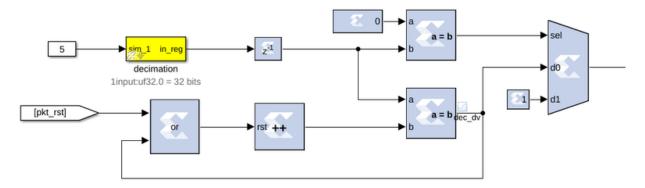

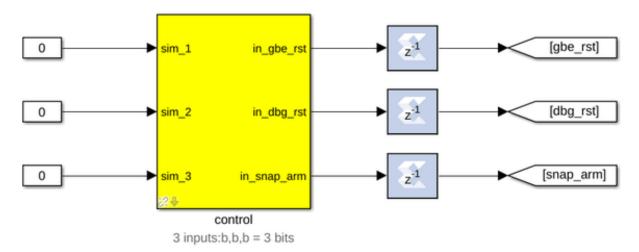

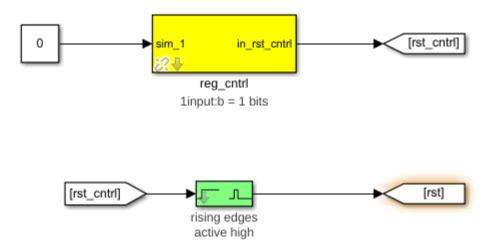

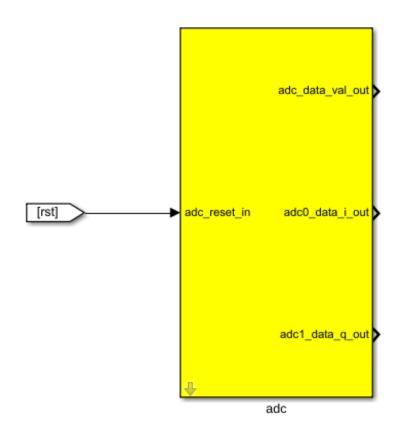

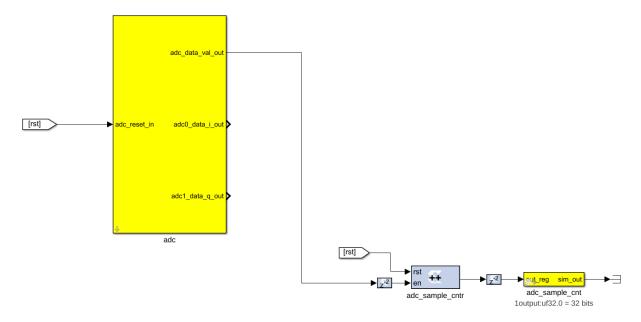

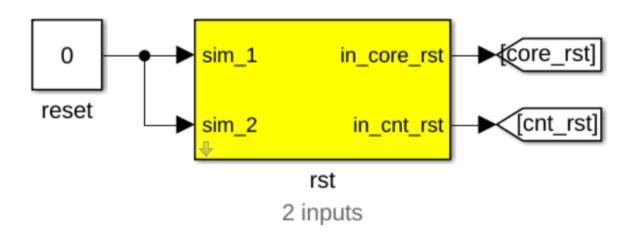

## Add reset logic

A very important piece of logic to consider when designing your system is how, when and what happens during reset. In this example we shall control our resets via a software register. We shall have two independent resets, one for the 10GbE cores which shall be used initially, and one to reset the user logic which may be used more often to restart the user part of the system. Construct reset circuitry as shown below.

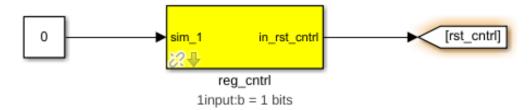

## Add a software register

Use a software register yellow block from the CASPER XPS System Blockset for the rst block. Rename it to rst.

It used to be that every register you inserted had to be natively 32-bits, and you were responsible for slicing these 32 bits into different signals if you want to control multiple flags. The latest block can implicitly break the 32-bit registers out into separate names signals, so we'll use that. The downside is there are a bunch of settings to configure – you need to set up the names and data types of your register subfields. You can configure the register as follows:

# 😣 💿 🛛 Block Parameters: rst

## swreg (mask)

A 32-bit software-accessible register. Can be divided into bitfields of varying widths and types using the fields in the block mask.

Setup I/O direction From Processor I/O delay 0 Initial Value 0 Sample period 1 Bitfield names [msb...lsb] [core\_rst cnt\_rst] Bitfield widths 36 **Chapter 1. Tutorial Instructions** [1 1]

## Add Goto blocks

Add two Goto blocks from Simulink->Signal Routing. Configure them to have the tags as shown (core\_rst and cnt\_rst). These tags will be used by associated From (also found in Simulink->Signal Routing) blocks in other parts of the design. These help to reduce clutter in your design and are useful for control signals that are routed to many destinations. They should not be used a lot for data signals as it reduces the ease with which data flow can be seen through the system.

## Add 10GbE and associated registers for data transmission

We will now add the 10GbE block to transmit a counter at a programmable rate.

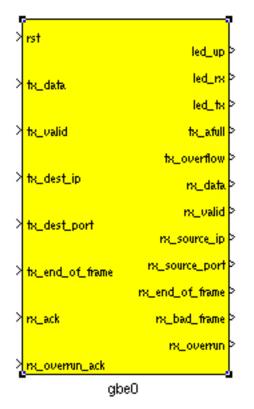

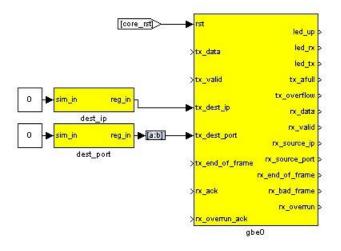

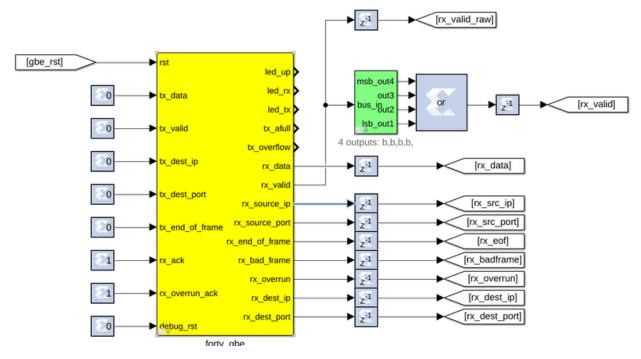

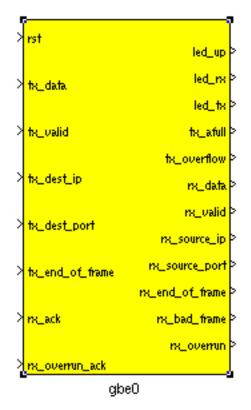

## Add a 10GbE block for data transmission

Add a ten\_GbE yellow block from the CASPER XPS System Blockset. It will be used to transmit data and we shall add another later to receive data. Rename it gbe0. Double click on the block to configure it and set it to be associated with SFP+ port 0. If your application can guarantee that it will be able to use received data straight away (as our application can), shallow receive buffers can be used to save resources. This optimisation is not necessary in this case as we will use a small fraction of resources in the FPGA.

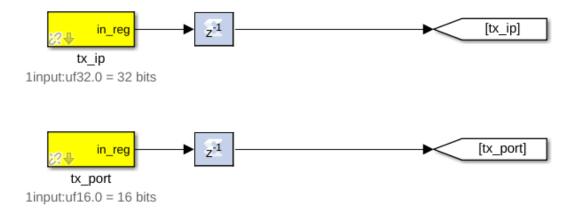

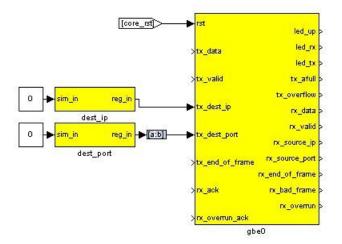

## Add registers to provide the target IP address and port number

Add two yellow-block software registers to provide the destination IP address and port number for transmission with the data. Name one dest\_ip and the other dest\_port. The registers should be configured to receive their values from

the processor. Connect them to the appropriate inputs of the gbe0 10GbE block as shown. A Slice block is required to use the lower 16 bits of data from the dest\_port register. Constant blocks from Simulink->Sources with 0 values are attached to the simulation inputs of the software registers. The destination port and IP address are not important in this system as it is a loopback example. Add a From block from Simulink->Signal Routing and set the tag to use core\_rst, this enables one to reset the block.

## Create a subsystem to generate a counter to transmit as data

We will now implement logic to generate a counter to transmit as data. This is already included in the Template for Tut 2. Some details are provided here for completeness.

## Construct a subsystem for data generation logic

It is often useful to group related functionality and hide the details. This reduces drawing space and complexity of the logic on the screen, making it easier to understand what is happening. Simulink allows the creation of Subsystems to accomplish this.

These can be copied to places where the same functionality is required or even placed in a library for use in other projects and by other people. To create a subsystem, one can highlight the logical elements to be encapsulated, then right-click and choose Create Subsystem from the list of options. You can also simply add a Subsystem block from Simulink->Ports & Subsystems.

Subsystems inherit variables from their parent system. Simulink allows one to create a variable whose scope is only a particular subsystem. To do this, right-click on a subsystem and choose the Create Mask option. The mask created for that particular subsystem allows one to add parameters that appear when you double-click on the icon associated with the subsystem.

The mask also allows you to associate an initialisation script with a particular subsystem. This script is called every time a mask parameter is modified and the Apply button clicked. It is especially useful if the internal structure of a subsystem must change based on mask parameters. Most of the interesting blocks in the CASPER library use these initialisation scripts.

Drop a subsystem block into your design and rename it pkt\_sim. Then double-click on it to add logic.

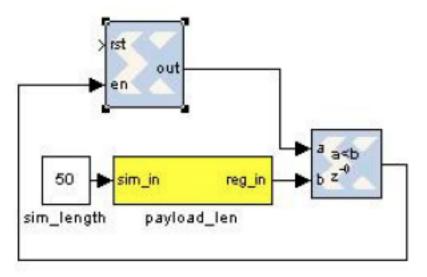

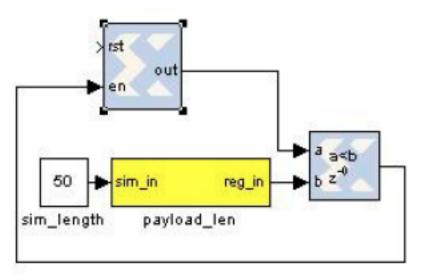

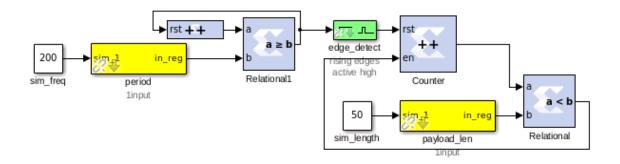

## Add a counter to generate a certain amount of data

Add a Counter block from Xilinx Blockset->Basic Elements and configure it to be unsigned, free-running, 32-bits, incrementing by 1 as shown. Add a Relational block, software register and Constant block as shown. In simulation

this circuit will generate a counter from 0 to 49 and then stop counting. This will allow us to generate 50 data elements before stopping.

| Counteril (             | Xilma Counter)                                                                                          | LID): |

|-------------------------|---------------------------------------------------------------------------------------------------------|-------|

|                         | <ol> <li>Free running counters are the<br/>ount limited counter is implement<br/>comparator.</li> </ol> |       |

| Basic Ad                | vanced Implementation                                                                                   |       |

| Counter type<br>Free Ru | nning C Count Limited                                                                                   |       |

| Count to value          | 1023                                                                                                    |       |

| Count directio          | n:<br>Down (° Up/Down                                                                                   |       |

| Initial solum           | 0                                                                                                       |       |

| Step                    | 1                                                                                                       |       |

| Output Pres             | aion                                                                                                    |       |

| Output type<br>C Signed | (<br>1 (Z's comp) 🧭 Unsigned                                                                            |       |

| Number of b             | 85 22                                                                                                   |       |

| Binary point            | D                                                                                                       |       |

| Optional Po             | ta -                                                                                                    |       |

| Provide I               | oad port                                                                                                |       |

| Provide                 | synchronous reset part                                                                                  |       |

| Provide a               | ervabile port                                                                                           |       |

| E-plot Sam              | ple Period                                                                                              |       |

| Sample perk             | nd source:<br>t                                                                                         |       |

| Explicit perio          | d 1                                                                                                     |       |

| OE                      | Cancel Help                                                                                             | Acoly |

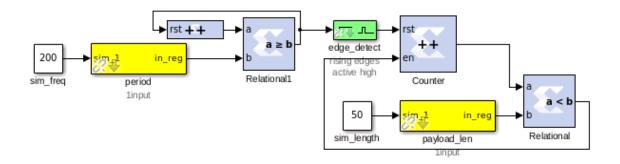

## Add a counter to limit the data rate

As mentioned earlier in this tutorial, it is impossible to supply data to the 10GbE transmission block at the full clock rate. This would mean transmitting a 64-bit word at 200MHz, and the 10GbE standard only supports up to 156.25MHz data transmission. We thus want to generate data in bursts such that the transmission FIFOs do not overflow. We thus add circuitry to limit the data rate as shown below. The logic that we have added on the left generates a reset at a fixed period determined by the software register. This will trigger the generation of a new packet of data as before. In simulation this allows us to limit the data rate to  $50/200 \times 200MHz = 50MHz$ . Using these values in actual hardware would limit the data rate to (50/(8/10\*156.25)) = 4Gbps.

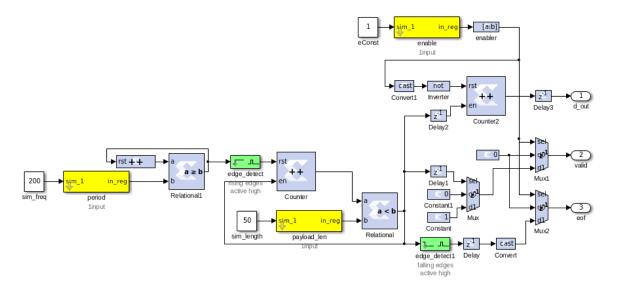

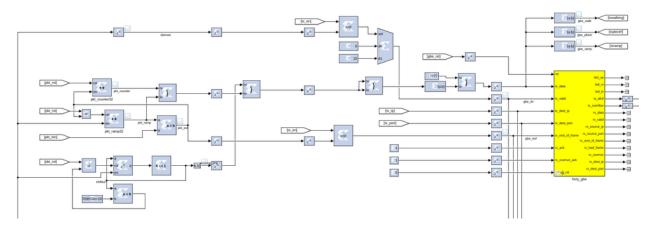

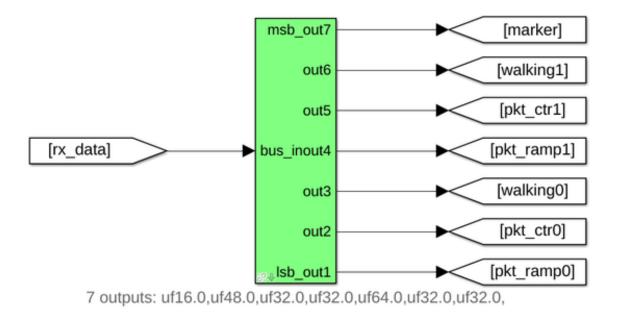

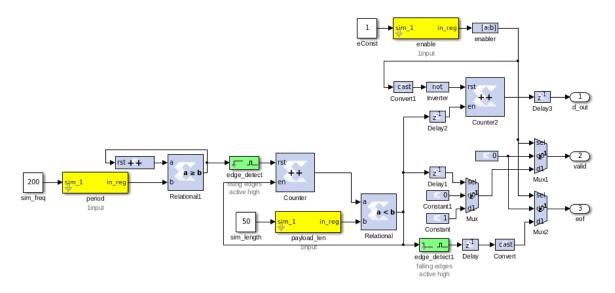

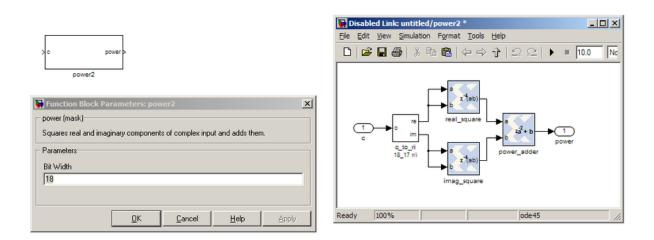

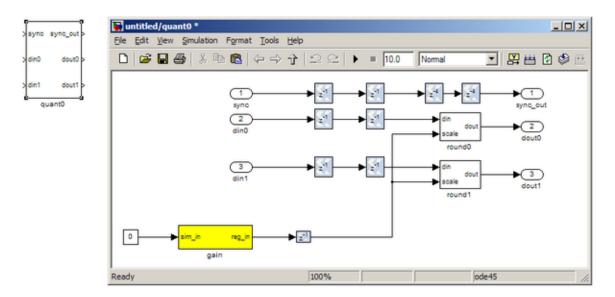

## Finalise logic including counter to be used as data

We will now finalise the data generation logic as shown below. To save time, use the existing logic provided with the tutorial. Counter1 in the illustration generates the actual data to be transmitted and the enable register allows this data stream to the transmitting 10GbE core to be turned off and on. Logic linked to the eof output port provides an indication to the 10GbE core that the final data word for the frame is being sent. This will trigger the core to begin transmission of the frame of data using the IP address and port number specified.

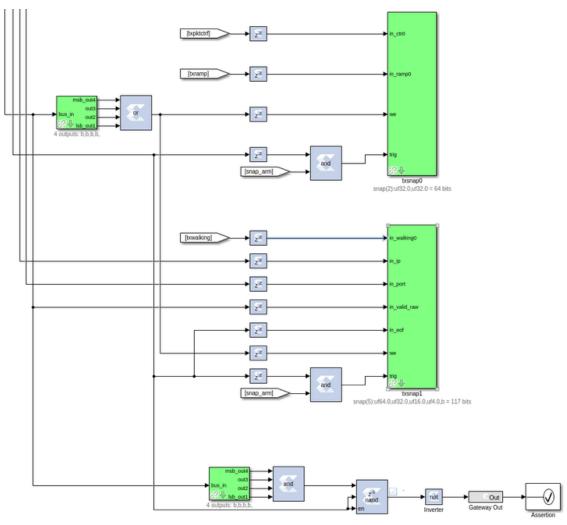

## **Receive blocks and logic**

The receive logic is is composed of another 10GbE yellow block with the transmission interface inputs all tied to 0 as no transmission is to be done, however Simulink requires all inputs to be connected. Connecting them to 0 should ensure that during synthesis the transmission logic for this 10GbE block is removed. Double click on the block to configure it and set it to be associated with SFP+ port 1.

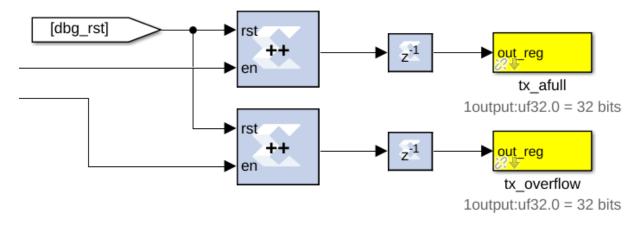

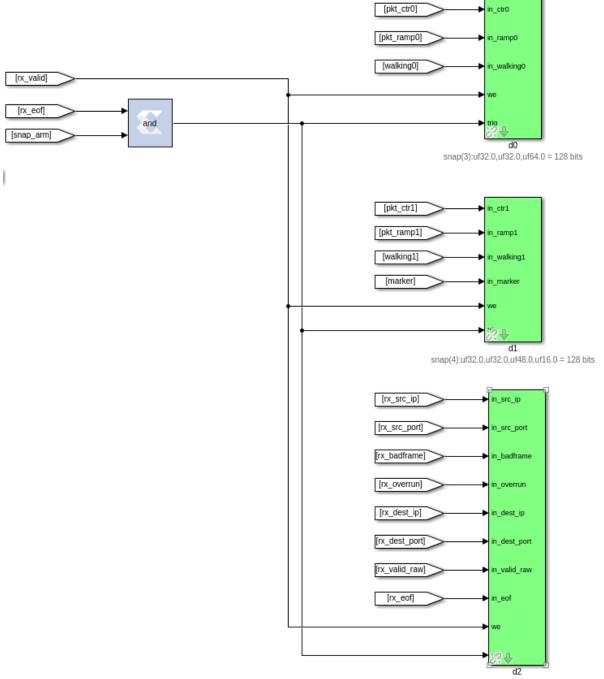

## Buffers to capture received and transmitted data

The casperfpga Python package contains all kinds of methods to interact with your 10GbE cores. For example, grabbing packets from the TX and RX stream, or counting the number of packets sent and received are all supported, as long as you turn on the appropriate functionality in the 10GbE yellow block. The settings we'll use are –

| 😣 💿 Block Parameters: gbe0                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ten_gbe (mask)                                                                                                                                                                                                                                                             |

| This block sends and receives UDP frames (packets). It accepts a 64 bit wide data stream with user-determined frame breaks. The data stream is wrapped in a UDP frame for transmission. Incoming UDP packets are unwrapped and the data presented as a 64 bit wide stream. |

| Core Debug counters                                                                                                                                                                                                                                                        |

| Port 0                                                                                                                                                                                                                                                                     |

| Shallow RX Fifo (Beware overruns!)                                                                                                                                                                                                                                         |

| ✓ Enable Large TX Frames (8k+512)                                                                                                                                                                                                                                          |

| ☑ Show Implementation Parameters                                                                                                                                                                                                                                           |

| Pre-emphasis 3                                                                                                                                                                                                                                                             |

| Differential swing 800 -                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                            |

| Fabric MAC Address                                                                                                                                                                                                                                                         |

| hex2dec('123456780000')                                                                                                                                                                                                                                                    |

| Fabric IP Address                                                                                                                                                                                                                                                          |

| 192*(2^24) + 168*(2^16) + 5*(2^8) + 20*(2^0)                                                                                                                                                                                                                               |

| Fabric UDP Port                                                                                                                                                                                                                                                            |

| 10000                                                                                                                                                                                                                                                                      |

| Fabric Gateway                                                                                                                                                                                                                                                             |

| 1                                                                                                                                                                                                                                                                          |

| ✓ Enable CPU RX                                                                                                                                                                                                                                                            |

| ✓ Enable CPU TX                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                            |

| <u>O</u> K <u>C</u> ancel <u>H</u> elp <u>A</u> pply                                                                                                                                                                                                                       |

| 😣 🗉 Block Parameters: gbe0                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ten_gbe (mask)                                                                                                                                                                                                                                                             |

| This block sends and receives UDP frames (packets). It accepts a 64 bit wide data stream with user-determined frame breaks. The data stream is wrapped in a UDP frame for transmission. Incoming UDP packets are unwrapped and the data presented as a 64 bit wide stream. |

| Core Debug counters                                                                                                                                                                                                                                                        |

| Debug counter width                                                                                                                                                                                                                                                        |

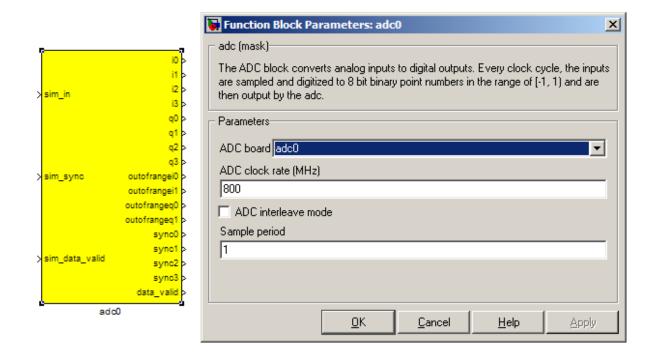

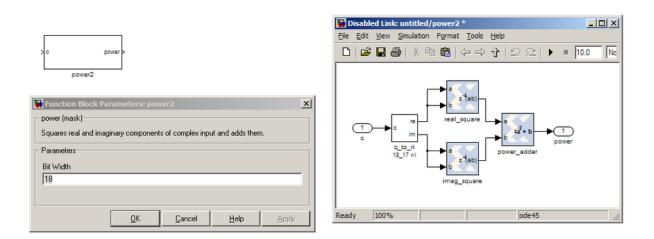

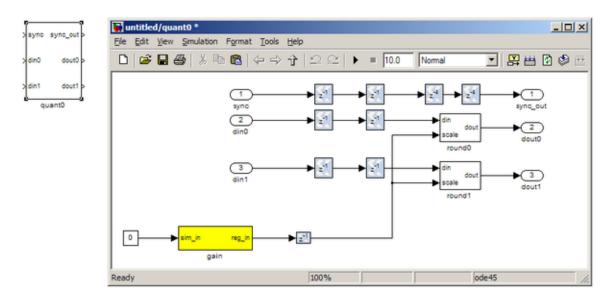

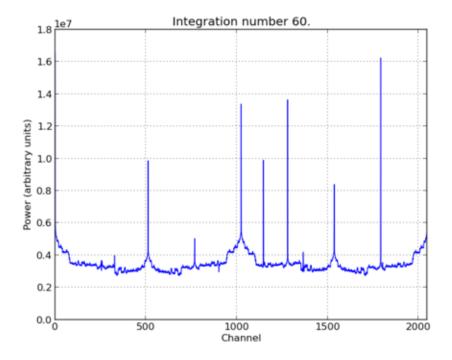

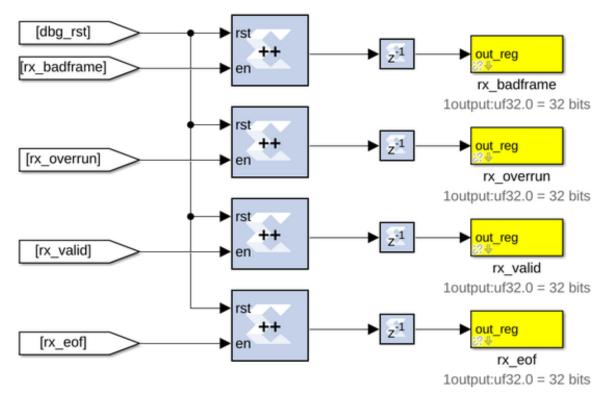

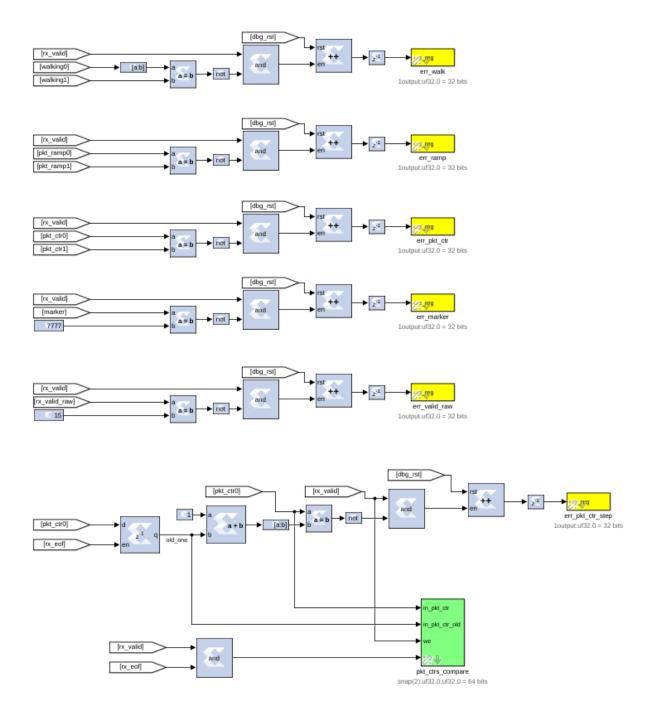

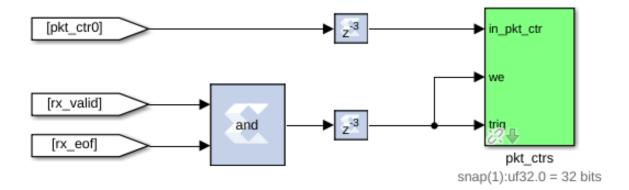

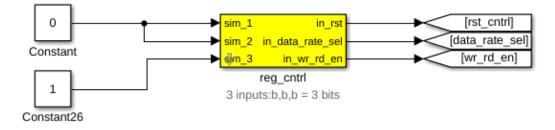

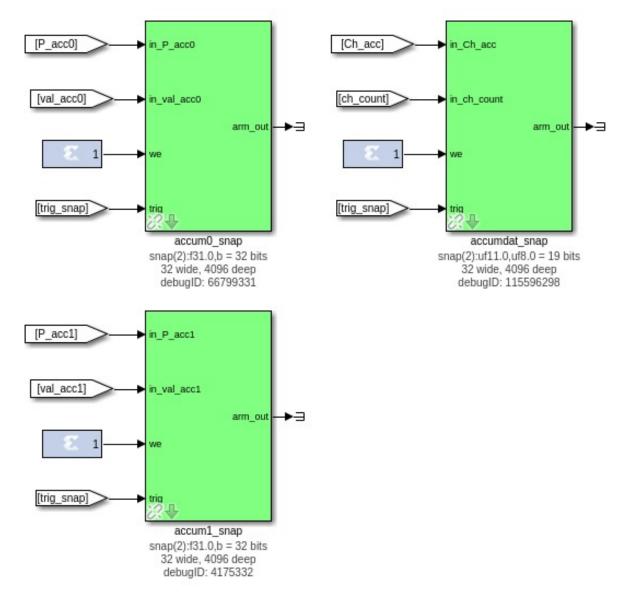

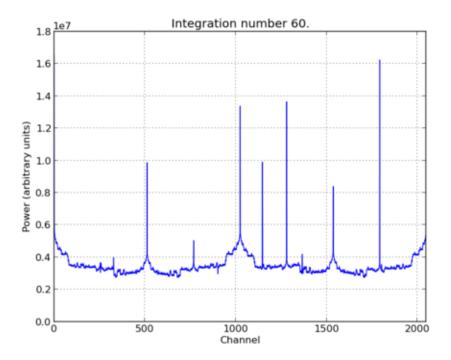

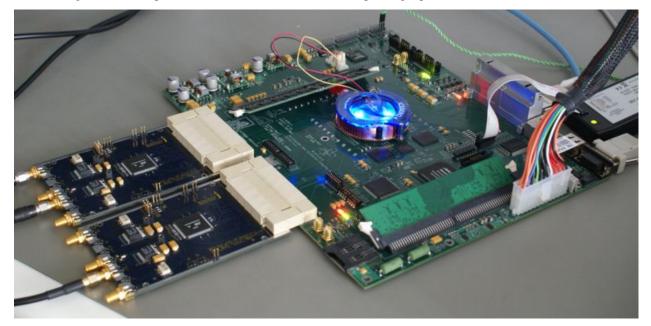

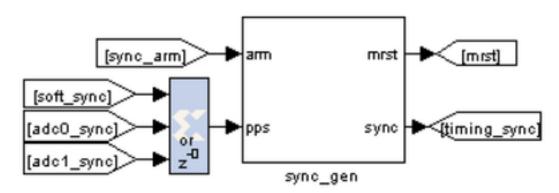

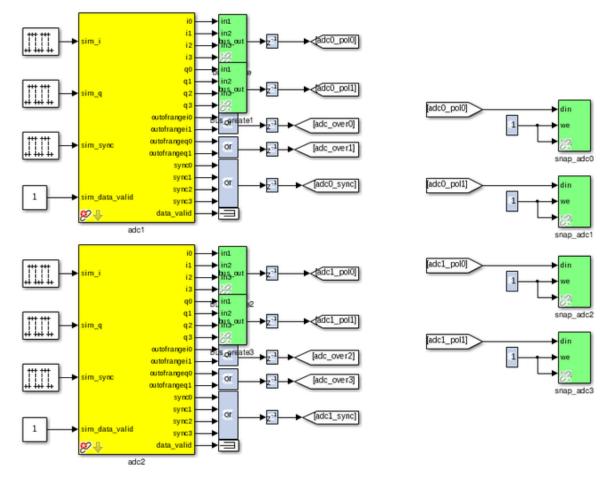

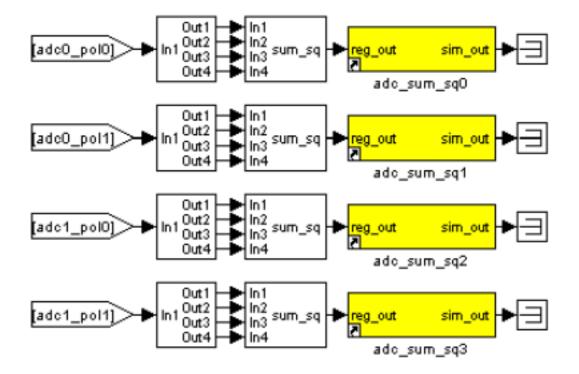

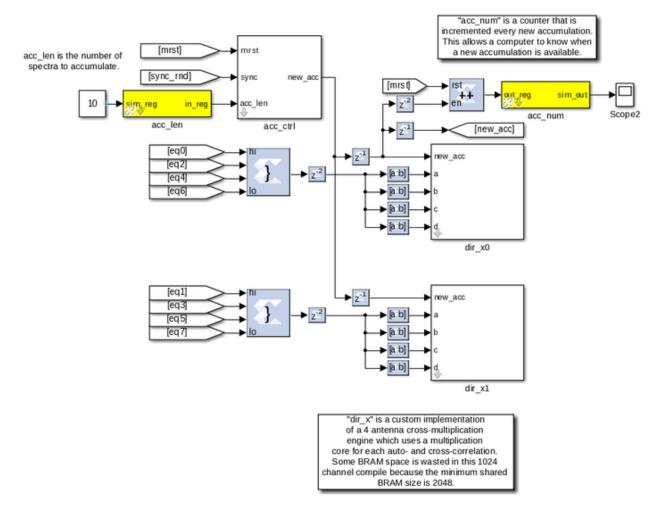

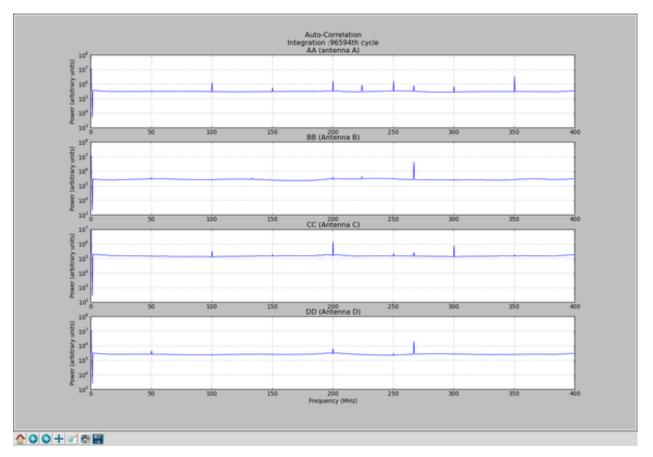

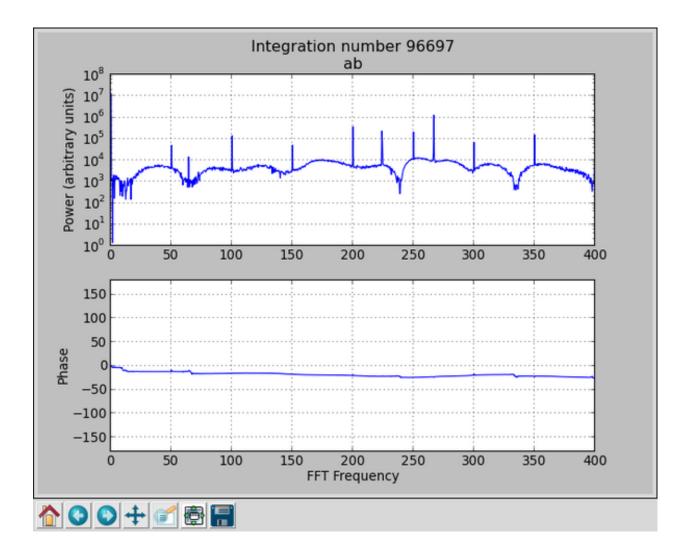

| 32                                                                                                                                                                                                                                                                         |